# IEM

# C/C++ Language Extensions for Cell Broadband Engine Architecture

Version 2.5

**CBEA JSRE Series**

Cell Broadband Engine Architecture Joint Software Reference Environment Series

February 27, 2008

© Copyright International Business Machines Corporation, Sony Computer Entertainment Incorporated, Toshiba Corporation 2002 - 2008

All Rights Reserved

Printed in the United States of America February 2008

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

IBM PowerPC

IBM Logo PowerPC Architecture

ibm.com

Cell Broadband Engine is a trademark of Sony Computer Entertainment, Inc.

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems and Technology Group 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at ibm.com

The IBM semiconductor solutions home page can be found at ibm.com/chips

February 27, 2008

# **Table of Contents**

| List of Tables                                                                | ix       |

|-------------------------------------------------------------------------------|----------|

| List of Figures                                                               | xii      |

| About This Document                                                           | xiv      |

| Audience                                                                      | xiv      |

| Version History                                                               | xiv      |

| Related Documentation                                                         | XX       |

| Conventions Used in This Document                                             | XX       |

| Data Types and Programming Directives                                         | 1        |

| 1.1. Data Types  1.1. Data Types                                              | 1        |

| 1.1.1. Fundamental Data Types                                                 | 1        |

| 1.1.2. Mapping of PPU Data Types to SPU Data Types                            | 1        |

| 1.1.3. Mapping of SPU Data Types to PPU Data Types                            | 2        |

| 1.2. Header Files                                                             | 2        |

| 1.2.1. Header File Contents                                                   | 2        |

| 1.2.2. Single Token Typedefs                                                  | 2        |

| 1.3. Alignment                                                                | 3        |

| 1.3.1. Default Data Type Alignments                                           | 3        |

| 1.3.2align_hint                                                               | 3        |

| 1.4. Operating on Vector Types                                                | 4        |

| 1.4.1. sizeof() Operator<br>1.4.2. Assignment Operator                        | 4<br>4   |

| 1.4.2. Assignment Operator  1.4.3. Address Operator                           | 4        |

| 1.4.4. Pointer Arithmetic and Pointer Dereferencing                           | 4        |

| 1.4.5. Type Casting                                                           | 5        |

| 1.4.6. Vector Literals                                                        | 5        |

| 1.5. Restrict Type Qualifier                                                  | 7        |

| 1.6. SPU Programmer Directed Branch Prediction                                | 7        |

| 1.7. Inline Assembly                                                          | 8        |

| 1.8. Target Definitions                                                       | 8        |

| 2. SPU Low-Level Specific and Generic Intrinsics                              | 9        |

| 2.1. Specific Intrinsics                                                      | 9        |

| 2.1.1. Specific Casting Intrinsics                                            | 12       |

| 2.2. Generic Intrinsics and Built-ins                                         | 13       |

| 2.2.1. Mapping Intrinsics with Scalar Operands                                | 13       |

| 2.2.2. Implicit Conversion of Arguments of Intrinsics                         | 14       |

| 2.2.3. Notations and Conventions                                              | 14       |

| 2.3. Constant Formation Intrinsics                                            | 15       |

| spu_splats: Splat Scalar to Vector                                            | 15<br>16 |

| 2.4. Conversion Intrinsics spu_convtf: Convert Integer Vector to Vector Float | 16       |

| spu_convts: Convert Vector Float to Signed Integer Vector                     | 16       |

| spu_convtu: Convert Vector Float to Unsigned Integer Vector                   | 16       |

| spu_extend: Extend Vector                                                     | 17       |

| spu_roundtf: Round Vector Double to Vector Float                              | 17       |

| 2.5. Arithmetic Intrinsics                                                    | 17       |

| spu_add: Vector Add                                                           | 17       |

| spu_addx: Vector Add Extended                                                 | 18       |

| spu_genb: Vector Generate Borrow                                              | 18       |

| spu_genbx: Vector Generate Borrow Extended<br>spu_genc: Vector Generate Carry | 18<br>19 |

| spu_genc: Vector Generate Carry spu_gencx: Vector Generate Carry Extended     | 19       |

| spu_madd: Vector Multiply and Add                                             | 19       |

| spu_mhhadd: Vector Multiply High High and Add                                 | 19       |

| . —                                                                           |          |

| spu_msub: Vector Multiply and Subtract                                                                                                  | 20             |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|

| spu_mul: Vector Multiply                                                                                                                | 20             |

| spu_mulh: Vector Multiply High                                                                                                          | 20             |

| spu_mule: Vector Multiply Even                                                                                                          | 21             |

| spu_mulo: Vector Multiply Odd                                                                                                           | 21             |

| spu_mulsr: Vector Multiply and Shift Right                                                                                              | 21             |

| spu_nmadd: Negative Vector Multiply and Add                                                                                             | 22             |

| spu_nmsub: Negative Vector Multiply and Subtract<br>spu_re: Vector Floating-Point Reciprocal Estimate                                   | 22<br>22       |

| spu_rsqrte: Vector Floating-Point Reciprocal Square Root Estimate                                                                       | 22             |

| spu_sub: Vector Subtract                                                                                                                | 23             |

| spu_subx: Vector Subtract Extended                                                                                                      | 23             |

| 2.6. Byte Operation Intrinsics                                                                                                          | 24             |

| spu_absd: Vector Absolute Difference                                                                                                    | 24             |

| spu_avg: Average of Two Vectors                                                                                                         | 24             |

| spu_sumb: Sum Bytes into Shorts                                                                                                         | 24             |

| 2.7. Compare, Branch and Halt Intrinsics                                                                                                | 24             |

| spu_bisled: Branch Indirect and Set Link if External Data                                                                               | 24             |

| spu_cmpabseq: Vector Compare Absolute Equal                                                                                             | 25             |

| spu_cmpabsgt: Vector Compare Absolute Greater Than                                                                                      | 25             |

| spu_cmpeq: Vector Compare Equal                                                                                                         | 26             |

| spu_cmpgt: Vector Compare Greater Than                                                                                                  | 27             |

| spu_hcmpeq: Halt If Compare Equal<br>spu_hcmpgt: Halt If Compare Greater Than                                                           | 28<br>28       |

| spu_testsv: Vector Test Special Value                                                                                                   | 28             |

| 2.8. Bits and Mask Intrinsics                                                                                                           | 29             |

| spu_cntb: Vector Count Ones for Bytes                                                                                                   | 29             |

| spu_cntlz: Vector Count Leading Zeros                                                                                                   | 29             |

| spu_gather: Gather Bits from Elements                                                                                                   | 29             |

| spu_maskb: Form Select Byte Mask                                                                                                        | 30             |

| spu_maskh: Form Select Halfword Mask                                                                                                    | 30             |

| spu_maskw: Form Select Word Mask                                                                                                        | 31             |

| spu_sel: Select Bits                                                                                                                    | 31             |

| spu_shuffle: Shuffle Two Vectors of Bytes                                                                                               | 31             |

| 2.9. Logical Intrinsics                                                                                                                 | 32             |

| spu_and: Vector Bit-Wise AND                                                                                                            | 32             |

| spu_andc: Vector Bit-Wise AND with Complement                                                                                           | 33<br>34       |

| spu_eqv: Vector Bit-Wise Equivalent spu_nand: Vector Bit-Wise Complement of AND                                                         | 34             |

| spu_nor: Vector Bit-Wise Complement of OR                                                                                               | 35             |

| spu_or: Vector Bit-Wise OR                                                                                                              | 35             |

| spu_orc: Vector Bit-Wise OR with Complement                                                                                             | 36             |

| spu_orx: OR Word Across                                                                                                                 | 36             |

| spu_xor: Vector Bit-Wise Exclusive OR                                                                                                   | 37             |

| 2.10. Shift and Rotate Intrinsics                                                                                                       | 37             |

| spu_rl: Vector Rotate Left by Bits                                                                                                      | 37             |

| spu_rlmask: Vector Rotate Left and Mask by Bits                                                                                         | 38             |

| spu_rlmaska: Vector Rotate Left and Mask Algebraic by Bits                                                                              | 39             |

| spu_rlmaskqw: Quadword Rotate Left and Mask by Bits                                                                                     | 40             |

| spu_rlmaskqwbyte: Quadword Rotate Left and Mask by Bytes<br>spu_rlmaskqwbytebc: Quadword Rotate Left and Mask by Bytes from Bit Shift C | 41<br>count 41 |

| spu_riqw: Quadword Rotate Left by Bits                                                                                                  | 42             |

| spu_rlqwbyte: Quadword Rotate Left by Bytes                                                                                             | 43             |

| spu_rlgwbytebc: Quadword Rotate Left by Bytes from Bit Shift Count                                                                      | 44             |

| spu_sl: Vector Shift Left by Bits                                                                                                       | 44             |

| spu_slqw: Quadword Shift Left by Bits                                                                                                   | 45             |

| spu_slqwbyte: Quadword Shift Left by Bytes                                                                                              | 45             |

| spu_slqwbytebc: Quadword Shift Left by Bytes from Bit Shift Count                                                                       | 46             |

| 2.11. Control Intrinsics                                                                                                                | 47             |

| spu_idisable: Disable Interrupts                                                                                                        | 47             |

| spu_ienable: Enable Interrupts                                                                                                          | 47             |

| spu_mffpscr: Move from Floating-Point Status and Control Register                                                                       | 48             |

| spu_mfspr: Move from Special Purpose Register                                            | 48             |

|------------------------------------------------------------------------------------------|----------------|

| spu_mtfpscr: Move to Floating-Point Status and Control Register                          | 48             |

|                                                                                          | 48             |

| spu_mtspr: Move to Special Purpose Register                                              |                |

| spu_dsync: Synchronize Data                                                              | 49             |

| spu_stop: Stop and Signal                                                                | 49             |

| spu_sync: Synchronize                                                                    | 49             |

| 2.12. Channel Control Intrinsics                                                         | 50             |

| spu_readch: Read Word Channel                                                            | 51             |

| spu_readchqw: Read Quadword Channel                                                      | 51             |

| spu_readchcnt: Read Channel Count                                                        | 51             |

| · =                                                                                      |                |

| spu_writech: Write Word Channel                                                          | 51             |

| spu_writechqw: Write Quadword Channel                                                    | 52             |

| 2.13. Scalar Intrinsics                                                                  | 52             |

| spu_extract: Extract Vector Element from Vector                                          | 52             |

| spu_insert: Insert Scalar into Specified Vector Element                                  | 53             |

| spu_promote: Promote Scalar to Vector                                                    | 54             |

| spu_promote. I formote ocalar to vector                                                  | J <del>4</del> |

| 3. Composite Intrinsics                                                                  | 56             |

| spu_mfcdma32: Initiate DMA to/from 32-Bit Effective Address                              | 56             |

| spu_mfcdma64: Initiate DMA to/from 64-Bit Effective Address                              | 56             |

|                                                                                          | 57             |

| spu_mfcstat: Read MFC Tag Status                                                         | 57             |

| 4. Programming Support for MFC Input and Output                                          | 58             |

|                                                                                          |                |

| 4.1. Structures                                                                          | 58             |

| mfc_list_element: DMA List Element for MFC List DMA                                      | 58             |

| 4.2. Effective Address Utilities                                                         | 58             |

| mfc_ea2h: Extract Higher 32 Bits from Effective Address                                  | 58             |

| mfc_ea2l: Extract Lower 32 Bits from Effective Address                                   | 58             |

| mfc_hl2ea: Concatenate Higher 32 Bits and Lower 32 Bits                                  | 59             |

| mfc_ceil128: Round Up Value to Next Multiple of 128                                      | 59             |

|                                                                                          |                |

| 4.3. MFC Tag Manager                                                                     | 59             |

| mfc_tag_reserve: Reserve a Tag for Exclusive Use                                         | 59             |

| mfc_tag_release: Release a Tag from Exclusive Use                                        | 60             |

| mfc_multi_tag_reserve: Reserve a Group of Tags for Exclusive Use                         | 60             |

| mfc_multi_tag_release: Release a Group of Tags from Exclusive Use                        | 60             |

| 4.4. MFC DMA Commands                                                                    | 60             |

| mfc_put: Move Data from Local Storage to Effective Address                               | 60             |

|                                                                                          |                |

| mfc_putb: Move Data from Local Storage to Effective Address with Barrier                 | 61             |

| mfc_putf: Move Data from Local Storage to Effective Address with Fence                   | 61             |

| mfc_get: Move Data from Effective Address to Local Storage                               | 61             |

| mfc_getf: Move Data from Effective Address to Local Storage with Fence                   | 61             |

| mfc_getb: Move Data from Effective Address to Local Storage with Barrier                 | 62             |

| 4.5. MFC List DMA Commands                                                               | 62             |

| mfc_putl: Move Data from Local Storage to Effective Address Using MFC List               | 62             |

|                                                                                          |                |

| mfc_putlb: Move Data from Local Storage to Effective Address Using MFC List with Barrier | 63             |

| mfc_putlf: Move Data from Local Storage to Effective Address Using MFC List with Fence   | 63             |

| mfc_getl: Move Data from Effective Address to Local Storage Using MFC List               | 63             |

| mfc_getlb: Move Data from Effective Address to Local Storage Using MFC List with Barrier | 63             |

| mfc_getlf: Move Data from Effective Address to Local Storage Using MFC List with Fence   | 64             |

| 4.6. MFC Atomic Update Commands                                                          | 64             |

| mfc_getllar: Get Lock Line and Create Reservation                                        | 64             |

| mfc_putllc: Put Lock Line if Reservation for Effective Address Exists                    | 64             |

|                                                                                          |                |

| mfc_putlluc: Put Lock Line Unconditional                                                 | 65             |

| mfc_putqlluc: Put Queued Lock Line Unconditional                                         | 65             |

| 4.7. MFC Synchronization Commands                                                        | 65             |

| mfc_sndsig: Send Signal                                                                  | 66             |

| mfc_sndsigb: Send Signal with Barrier                                                    | 66             |

| mfc_sndsigf: Send Signal with Fence                                                      | 66             |

| mfc_barrier: Enqueue mfc_barrier Command into DMA Queue or Stall When Queue is Full      | 66             |

|                                                                                          | 67             |

| mfc_eieio: Enqueue mfc_eieio Command into DMA Queue or Stall When Queue is Full          |                |

| mfc_sync: Enqueue mfc_sync Command into DMA Queue or Stall When Queue is Full            | 67             |

| 4.8. MFC DMA Status                                                                      | 67             |

|                                                                                          |                |

| mfc_stat_cmd_queue: Check the Number of Available Entries in the MFC DMA Queue mfc_write_tag_mask: Set Tag Mask to Select MFC Tag Groups to be Included in Query           | 67       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Operation  mfc_read_tag_mask: Read Tag Mask Indicating MFC Tag Groups to be Included in Query                                                                              | 67       |

| Operation                                                                                                                                                                  | 67       |

| mfc_write_tag_update: Request That Tag Status be Updated                                                                                                                   | 68       |

| mfc_write_tag_update_immediate: Request That Tag Status be Immediately Updated                                                                                             | 68       |

| mfc_write_tag_update_any: Request That Tag Status be Updated for Any Enabled Completic                                                                                     |          |

| with No Outstanding Operation                                                                                                                                              | 68       |

| mfc_write_tag_update_all: Request That Tag Status be Updated When All Enabled Tag Grou                                                                                     |          |

| Have No Outstanding Operation<br>mfc_stat_tag_update: Check Availability of Tag Status Update Request Channel                                                              | 68<br>68 |

| mfc_read_tag_status: Wait for an Updated Tag Status                                                                                                                        | 69       |

| mfc_read_tag_status_immediate: Wait for the Updated Status of Any Enabled Tag Group                                                                                        | 69       |

| mfc_read_tag_status_any: Wait for No Outstanding Operation of Any Enabled Tag Group                                                                                        | 69       |

| mfc_read_tag_status_all: Wait for No Outstanding Operation of All Enabled Tag Groups                                                                                       | 69       |

| mfc_stat_tag_status: Check Availability of MFC_RdTagStat Channel                                                                                                           | 69       |

| mfc_read_list_stall_status: Read List DMA Stall-and-Notify Status                                                                                                          | 70       |

| mfc_stat_list_stall_status: Check Availability of List DMA Stall-and-Notify Status<br>mfc_write_list_stall_ack: Acknowledge Tag Group Containing Stalled DMA List Commands | 70<br>70 |

| mfc_read_atomic_status: Read Atomic Command Status                                                                                                                         | 70       |

| mfc_stat_atomic_status: Check Availability of Atomic Command Status                                                                                                        | 70       |

| 4.9. MFC Multisource Synchronization Request                                                                                                                               | 71       |

| mfc_write_multi_src_sync_request: Request Multisource Synchronization                                                                                                      | 71       |

| mfc_stat_multi_src_sync_request: Check the Status of Multisource Synchronization                                                                                           | 71       |

| 4.10. SPU Signal Notification                                                                                                                                              | 71       |

| spu_read_signal1: Atomically Read and Clear Signal Notification 1 Channel                                                                                                  | 71       |

| spu_stat_signal1: Check if Pending Signals Exist on Signal Notification 1 Channel                                                                                          | 71       |

| spu_read_signal2: Atomically Read and Clear Signal Notification 2 Channel<br>spu_stat_signal2: Check if Pending Signals Exist on Signal Notification 2 Channel             | 72<br>72 |

| 4.11. SPU Mailboxes                                                                                                                                                        | 72       |

| spu_read_in_mbox: Read Next Data Entry in SPU Inbound Mailbox                                                                                                              | 72       |

| spu_stat_in_mbox: Get the Number of Data Entries in SPU Inbound Mailbox                                                                                                    | 72       |

| spu_write_out_mbox: Send Data to SPU Outbound Mailbox                                                                                                                      | 72       |

| spu_stat_out_mbox: Get Available Capacity of SPU Outbound Mailbox                                                                                                          | 73       |

| spu_write_out_intr_mbox: Send Data to SPU Outbound Interrupt Mailbox                                                                                                       | 73       |

| spu_stat_out_intr_mbox: Get Available Capacity of SPU Outbound Interrupt Mailbox                                                                                           | 73       |

| 4.12. SPU Decrementer                                                                                                                                                      | 73       |

| spu_read_decrementer: Read Current Value of Decrementer<br>spu_write_decrementer: Load a Value to Decrementer                                                              | 73<br>73 |

| 4.13. SPU Event                                                                                                                                                            | 74       |

| spu_read_event_status: Read Event Status or Stall Until Status is Available                                                                                                | 74       |

| spu_stat_event_status: Check Availability of Event Status                                                                                                                  | 74       |

| spu_write_event_mask: Select Events to be Monitored by Event Status                                                                                                        | 74       |

| spu_write_event_ack: Acknowledge Events                                                                                                                                    | 75       |

| spu_read_event_mask: Read Event Status Mask                                                                                                                                | 75<br>75 |

| 4.14. SPU State Management  spu_read_machine_status: Read Current SPU Machine Status                                                                                       | 75<br>75 |

| spu_read_machine_status. Read Current SPO Machine Status spu_write_srr0: Write to SPU SRR0                                                                                 | 75<br>75 |

| spu_read_srr0: Read SPU SRR0                                                                                                                                               | 75       |

| . – –                                                                                                                                                                      |          |

| 5. SPU and PPU Vector Multimedia Extension Intrinsics                                                                                                                      | 76       |

| 5.1. Mapping of PPU VMX Intrinsics to SPU Intrinsics 5.1.1. One-to-One Mapped Intrinsics                                                                                   | 76<br>76 |

| 5.1.1. Offe-to-Offe Mapped Intrinsics  5.1.2. PPU VMX Intrinsics That Are Difficult to Map to SPU Intrinsics                                                               | 77       |

| 5.2. Mapping of SPU Intrinsics to PPU VMX Intrinsics                                                                                                                       | 77       |

| 5.2.1. One-to-One Mapped Intrinsics                                                                                                                                        | 78       |

| 5.2.2. SPU Intrinsics That Are Difficult to Map to PPU VMX Intrinsics                                                                                                      | 78       |

| 6. PPU Specific Intrinsics                                                                                                                                                 | 80       |

| cctph: Change Thread Priority to High                                                                                                                                      | 80       |

| cctpl: Change Thread Priority to Low                                                                                                                                       | 80       |

|                                                                                                                                                                            |          |

| cctpm: Change Thread Priority to Medium                                        | 80                   |

|--------------------------------------------------------------------------------|----------------------|

| cntlzd: Count Leading Doubleword Zeros                                         | 81                   |

| cntlzw: Count Leading Word Zeros                                               | 81                   |

| db10cyc: Delay 10 Cycles at Dispatch                                           | 81                   |

|                                                                                | _                    |

| db12cyc: Delay 12 Cycles at Dispatch                                           | 81                   |

| db16cyc: Delay 16 Cycles at Dispatch                                           | 82                   |

| db8cyc: Delay 8 Cycles at Dispatch                                             | 82                   |

| dcbf: Data Cache Block Flush                                                   | 82                   |

| dcbst: Data Cache Block Store                                                  | 82                   |

| dcbt: Data Cache Block Touch                                                   | 83                   |

| dcbt_TH1000: Set Up Streaming Data                                             | 83                   |

| dcbt_TH1010: Start or Stop Streaming Data                                      | 83                   |

| dcbtst: Data Cache Block Touch for Store                                       | 84                   |

| dcbz: Data Cache Block Set to Zero                                             | 84                   |

| eieio: Enforce In-Order Execution of I/O                                       | 84                   |

| fabs: Double Absolute Value                                                    | 85                   |

| fabsf: Float Absolute Value                                                    | 85                   |

| fcfid: Convert Doubleword to Double                                            | 85                   |

| fctid: Convert Double to Doubleword                                            | 85                   |

| fctidz: Convert Double to Doubleword with Round Towards Zero                   | 86                   |

| fctiw: Convert Double to Word                                                  | 86                   |

| fctiwz: Convert Double to Word with Round Towards Zero                         | 86                   |

| fmadd: Double Fused Multiply and Add                                           | 86                   |

| fmadd: Bouble I dised Multiply and Add<br>fmadds: Float Fused Multiply and Add | 87                   |

|                                                                                | 87<br>87             |

| fmsub: Double Fused Multiply and Subtract                                      |                      |

| fmsubs: Float Fused Multiply and Subtract                                      | 87                   |

| fmul: Double Multiply                                                          | 87                   |

| fmuls: Float Multiply                                                          | 88                   |

| fnabs: Double Negative                                                         | 88                   |

| fnabsf: Float Negative                                                         | 88                   |

| fnmadd: Double Fused Negative Multiply and Add                                 | 88                   |

| fnmadds: Float Fused Negative Multiply and Add                                 | 89                   |

| fnmsub: Double Fused Negative Multiply and Subtract                            | 89                   |

| fnmsubs: Float Fused Negative Multiply and Subtract                            | 89                   |

| fres: Float Reciprocal Estimate                                                | 89                   |

| frsp: Round to Single Precision                                                | 90                   |

| frsqrte: Double Reciprocal Square Root Estimate                                | 90                   |

| fsel: Floating-Point Select of Double                                          | 90                   |

| fsels: Floating-Point Select of Float                                          | 90                   |

| fsqrt: Double Square Root                                                      | 91                   |

| fsqrts: Float Square Root                                                      | 91                   |

| icbi: Instruction Cache Block Invalidate                                       | 91                   |

| isync: Instruction Sync                                                        | 91                   |

| Idarx: Load Doubleword with Reserved                                           | 92                   |

| Idbrx: Load Reversed Doubleword                                                | 92                   |

| Ihbrx: Load Reversed Halfword                                                  | 92                   |

| Iwarx: Load Word with Reserved                                                 | 92                   |

| Iwbrx: Load Reversed Word                                                      | 93                   |

| lwsync: Light Weight Sync                                                      | 93                   |

| mffs: Move from Floating-Point Status and Control Register                     | 93                   |

| mfspr: Move from Special Purpose Register                                      | 93                   |

| mftb: Move from Time Base                                                      | 94                   |

| mtfsb0: Reset Bit of FPSCR                                                     | 9 <del>4</del><br>94 |

| mtfsb1: Set Bit of FPSCR                                                       | 94                   |

|                                                                                | _                    |

| mtfsf: Set Fields in FPSCR                                                     | 94                   |

| mtfsfi: Set Field of FPSCR                                                     | 95                   |

| mtspr: Move to Special Purpose Register                                        | 95                   |

| mulhd: Multiply Doubleword, High Part                                          | 95                   |

| mulhdu: Multiply Double Unsigned Word, High Part                               | 95                   |

| mulhw: Multiply Word, High Part                                                | 96                   |

| mulhwu: Multiply Unsigned Word, High Part                                      | 96                   |

| nop: No Operation                                                              | 96                   |

|                                                                                |                      |

|                                                                            | 00  |

|----------------------------------------------------------------------------|-----|

| protected_stream_count: Set the Number of Blocks to Stream                 | 96  |

| protected_stream_go: Start All Streams                                     | 96  |

| protected_stream_set: Set Up a Stream                                      | 96  |

| protected_stream_stop: Stop a Stream                                       | 97  |

| protected_stream_stop_all: Stop All Streams                                | 97  |

|                                                                            |     |

| protected_unlimited_stream_set: Set Up an Unlimited Stream                 | 97  |

| rldcl: Rotate Left Doubleword then Clear Left                              | 97  |

| rldcr: Rotate Left Doubleword then Clear Right                             | 98  |

| rldic: Rotate Left Doubleword Immediate then Clear                         | 98  |

| rldicl: Rotate Left Doubleword Immediate then Clear Left                   | 98  |

| rldicr: Rotate Left Doubleword Immediate then Clear Right                  | 99  |

|                                                                            |     |

| rldimi: Rotate Left Doubleword Immediate then Mask Insert                  | 99  |

| rlwimi: Rotate Left Word Immediate then Mask Insert                        | 99  |

| rlwinm: Rotate Left Word Immediate then AND With Mask                      | 100 |

| rlwnm: Rotate Left Word then AND With Mask                                 | 100 |

| setflm: Save and Set the FPSCR                                             | 100 |

| stdbrx: Store Reversed Doubleword                                          | 100 |

| stdcx: Store Doubleword Conditional                                        |     |

|                                                                            | 101 |

| sthbrx: Store Reversed Halfword                                            | 101 |

| stwbrx: Store Reversed Word                                                | 101 |

| _stwcx: Store Word Conditional                                             | 102 |

| sync: Sync                                                                 | 102 |

|                                                                            |     |

| 7. PPU Vector Multimedia Extension Intrinsics                              | 104 |

| vec extract: Extract Vector Element from Vector                            | 105 |

| vec_insert: Insert Scalar into Specified Vector Element                    | 106 |

|                                                                            |     |

| vec_lvlx: Load Vector Left Indexed                                         | 107 |

| vec_lvlxl: Load Vector Left Indexed Last                                   | 108 |

| vec_lvrx: Load Vector Right Indexed                                        | 109 |

| vec_lvrxl: Load Vector Right Indexed Last                                  | 110 |

| vec stylx: Store Vector Left Indexed                                       | 111 |

| vec_stvlxl: Store Vector Left Indexed Last                                 | 112 |

| vec_stvrx: Store Vector Right Indexed                                      | 113 |

|                                                                            |     |

| vec_stvrxl: Store Vector Right Indexed Last                                | 114 |

| vec_promote: Promote Scalar to Vector                                      | 115 |

| vec_splats: Splat Scalar to Vector                                         | 115 |

|                                                                            | 440 |

| 8. SPU C and C++ Standard Libraries and Language Support                   | 116 |

| 8.1. Standard Libraries                                                    | 116 |

| 8.1.1. C Standard Library                                                  | 116 |

| 8.1.2. C++ Standard Library                                                | 119 |

| ·                                                                          |     |

| 8.2. Non-Supported Language Features                                       | 120 |

| 9. Floating-Point Arithmetic on the SPU                                    | 122 |

| <del>-</del>                                                               |     |

| 9.1. Properties of Floating-Point Data Type Representations                | 122 |

| 9.2. Floating-Point Environment                                            | 123 |

| 9.2.1. Rounding Modes                                                      | 123 |

| 9.2.2. Floating-Point Exceptions                                           | 123 |

| 9.2.3. Other Floating-Point Constants in math.h                            | 125 |

|                                                                            |     |

| 9.3. Floating-Point Operations                                             | 125 |

| 9.3.1. Floating-Point Conversions                                          | 125 |

| 9.3.2. Overall Behavior of C Operators and Standard Library Math Functions | 126 |

| 9.3.3. Floating-Point Expression Special Cases                             | 127 |

| 9.3.4. Specific Behavior of Standard Math Functions                        | 128 |

| ·                                                                          | .20 |

| 10. Operator Overloading for Vector Data Types                             | 130 |

| 10.1. Supported Types                                                      | 130 |

|                                                                            |     |

| 10.2. Vector Subscripting                                                  | 130 |

| 10.3. Unary Operators                                                      | 130 |

| 10.4. Binary Operators                                                     | 131 |

| 10.5. Relational Operators                                                 | 131 |

| . Jos Molational Operators                                                 | 101 |

Index 132

## **List of Tables**

| Table 1-1: Vector Data Types                                                              | 1  |

|-------------------------------------------------------------------------------------------|----|

| Table 1-2: Non-identical Mapping of PPU VMX Data Types to SPU Data Types                  | 2  |

| Table 1-3: Non-identical Mapping of SPU Data Types to PPU VMX Data Types                  | 2  |

| Table 1-4: Single Token Vector Data Types                                                 | 2  |

| Table 1-5: Default Data Type Alignments                                                   | 3  |

| Table 1-6: Vector Pointer Types and Matching Base Element Pointer Types                   | 5  |

| Table 1-7: Vector Literal Format and Description                                          | 6  |

| Table 1-8: Alternate Vector Literal Format and Description                                | 6  |

| Table 2-9: Assembly Instructions for which No Specific Intrinsic Exists                   | 9  |

| Table 2-10: Specific Intrinsics Not Accessible Through Generic Intrinsics                 | 10 |

| Table 2-11: Specific Casting Intrinsics                                                   | 13 |

| Table 2-12: Possible Uses of Immediate Load Instructions for Various Values of Constant b | 14 |

| Table 2-13: Splat Scalar to Vector                                                        | 15 |

| Table 2-14: Convert Integer Vector to Vector Float                                        | 16 |

| Table 2-15: Convert Vector Float to Signed Integer Vector                                 | 16 |

| Table 2-16: Convert Vector Float to Unsigned Integer Vector                               | 16 |

| Table 2-17: Extend Vector                                                                 | 17 |

| Table 2-18: Round Vector Double to Vector Float                                           | 17 |

| Table 2-19: Vector Add                                                                    | 17 |

| Table 2-20: Vector Add Extended                                                           | 18 |

| Table 2-21: Vector Generate Borrow                                                        | 18 |

| Table 2-22: Vector Generate Borrow Extended                                               | 18 |

| Table 2-23: Vector Generate Carry                                                         | 19 |

| Table 2-24: Vector Generate Carry Extended                                                | 19 |

| Table 2-25: Vector Multiply and Add                                                       | 19 |

| Table 2-26: Vector Multiply High High and Add                                             | 20 |

| Table 2-27: Vector Multiply and Subtract                                                  | 20 |

| Table 2-28: Vector Multiply                                                               | 20 |

| Table 2-29: Vector Multiply High                                                          | 20 |

| Table 2-30: Vector Multiply Even                                                          | 21 |

| Table 2-31: Vector Multiply Odd                                                           | 21 |

| Table 2-32: Vector Multiply and Shift Right                                               | 21 |

| Table 2-33: Negative Vector Multiply and Add                                              | 22 |

| Table 2-34: Negative Vector Multiply and Subtract                                         | 22 |

| Table 2-35: Vector Floating-Point Reciprocal Estimate                                     | 22 |

| Table 2-36: Vector Floating-Point Reciprocal Square Root Estimate                         | 22 |

| Table 2-37: Vector Subtract                                                               | 23 |

| Table 2-38: Vector Subtract Extended                                                      | 23 |

| Table 2-39: Vector Absolute Difference                                                    | 24 |

| Table 2-40: Average of Two Vectors                                                        | 24 |

| Table 2-41: Sum Bytes into Shorts                                                         | 24 |

| Table 2-42: Branch Indirect and Set Link if External Data                                 | 25 |

| Table 2-43: Vector Compare Absolute Equal                                                 | 25 |

| Table 2-44: Vector Compare Absolute Greater Than                                          | 25 |

| Table 2-45: Vector Compare Equal                                                          | 26 |

| Table 2-46: Vector Compare Greater Than                                                   | 27 |

| Table 2-47: Halt If Compare Equal                                                         | 28 |

| Table 2-48: Halt If Compare Greater Than                                                  | 28 |

| Table 2-49: Vector Test Special Value                                                     | 28 |

| Table 2-50: Special Value Bit Flag Mnemonics                                              | 28 |

| Table 2-51: Vector Count Ones for Bytes                                                   | 29 |

| Table 2-52: Vector Count Leading Zeros                                                    | 29 |

| Table 2-53: Gather Bits from Elements                                                     | 30 |

| Table 2-54: Form Select Byte Mask                                                         | 30 |

| Table 2-55: Form Select Halfword Mask                                                     | 30 |

| Table 2-56: Form Select Word Mask                                                         | 31 |

| Table 2-57: Select Bits                                                                   | 31 |

Χ

# IBM

| Table 2-58: | Shuffle Two Vectors of Bytes                                      | 32 |

|-------------|-------------------------------------------------------------------|----|

| Table 2-59: | Vector Bit-Wise AND                                               | 32 |

| Table 2-60: | Vector Bit-Wise AND with Complement                               | 33 |

| Table 2-61: | Vector Bit-Wise Equivalent                                        | 34 |

| Table 2-62: | Vector Bit-Wise Complement of AND                                 | 34 |

| Table 2-63: | Vector Bit-Wise Complement of OR                                  | 35 |

| Table 2-64: | Vector Bit-Wise OR                                                | 35 |

| Table 2-65: | Vector Bit-Wise OR with Complement                                | 36 |

|             | OR Word Across                                                    | 36 |

| Table 2-67: | Vector Bit-Wise Exclusive OR                                      | 37 |

| Table 2-68: | Vector Rotate Left by Bits                                        | 37 |

| Table 2-69: | Vector Rotate Left and Mask by Bits                               | 38 |

| Table 2-70: | Vector Rotate Left and Mask Algebraic by Bits                     | 39 |

|             | Quadword Rotate Left and Mask by Bits                             | 40 |

| Table 2-72: | Quadword Rotate Left and Mask by Bytes                            | 41 |

|             | Quadword Rotate Left and Mask by Bytes from Bit Shift Count       | 42 |

| Table 2-74: | Quadword Rotate Left by Bits                                      | 42 |

| Table 2-75: | Quadword Rotate Left by Bytes                                     | 43 |

| Table 2-76: | Quadword Rotate Left by Bytes from Bit Shift Count                | 44 |

| Table 2-77: | Vector Shift Left by Bits                                         | 44 |

| Table 2-78: | Quadword Shift Left by Bits                                       | 45 |

| Table 2-79: | Quadword Shift Left by Bytes                                      | 45 |

|             | Quadword Shift Left by Bytes from Bit Shift Count                 | 46 |

| Table 2-81: | Disable Interrupts                                                | 47 |

|             | Enable Interrupts                                                 | 47 |

| Table 2-83: | Move from Floating-Point Status and Control Register              | 48 |

|             | Move from Special Purpose Register                                | 48 |

| Table 2-85: | Move to Floating-Point Status and Control Register                | 48 |

|             | Move to Special Purpose Register                                  | 49 |

|             | Synchronize Data                                                  | 49 |

|             | Stop and Signal                                                   | 49 |

|             | Synchronize                                                       | 49 |

| Table 2-90: | SPU Channel Numbers                                               | 50 |

| Table 2-91: | MFC Channel Numbers                                               | 50 |

| Table 2-92: | Read Word Channel                                                 | 51 |

| Table 2-93: | Read Quadword Channel                                             | 51 |

| Table 2-94: | Read Channel Count                                                | 51 |

| Table 2-95: | Write Word Channel                                                | 51 |

| Table 2-96: | Write Quadword Channel                                            | 52 |

| Table 2-97: | Extract Vector Element from Vector                                | 52 |

| Table 2-98: | Insert Scalar into Specified Vector Element                       | 53 |

| Table 2-99: | Promote Scalar to Vector                                          | 54 |

| Table 3-100 | 2: Initiate DMA to/from 32-Bit Effective Address                  | 56 |

| Table 3-101 | I: Initiate DMA to/from 64-Bit Effective Address                  | 56 |

| Table 3-102 | 2: Read MFC Tag Status                                            | 57 |

| Table 4-103 | 3: MFC Tag Manager Mnemonics                                      | 59 |

| Table 4-104 | 1: MFC DMA Command Mnemonics                                      | 60 |

| Table 4-105 | 5: MFC List DMA Command Mnemonics                                 | 62 |

| Table 4-106 | S: MFC Atomic Update Command Mnemonics                            | 64 |

| Table 4-107 | 7: MFC Synchronization Command Mnemonics                          | 65 |

| Table 4-108 | 3: MFC Write Tag Update Conditions                                | 68 |

| Table 4-109 | 9: Read Atomic Command Status or Stall Until Status Is Available  | 70 |

|             | ): MFC Event Bit-Fields                                           | 74 |

| Table 5-111 | I: PPU VMX Intrinsics That Map One-to-One with SPU Intrinsics     | 77 |

| Table 5-112 | 2: PPU VMX Intrinsics That Are Difficult to Map to SPU Intrinsics | 77 |

| Table 5-113 | 3: SPU Intrinsics That Map One-to-One with PPU VMX Intrinsics     | 78 |

| Table 5-114 | 4: SPU Intrinsics That Are Difficult to Map to PPU VMX Intrinsics | 78 |

|             | 5: Change Thread Priority to High                                 | 80 |

| Table 6-116 | S: Change Thread Priority to Low                                  | 80 |

| Table 6-117 | 7: Change Thread Priority to Medium                               | 80 |

|             | 3: Count Leading Doubleword Zeros                                 | 81 |

|             | 9: Count Leading Word Zeros                                       | 81 |

| Table 6-120: Delay 10 Cycles at Dispatch                          | 81 |

|-------------------------------------------------------------------|----|

| Table 6-121: Delay 12 Cycles at Dispatch                          | 81 |

| Table 6-122: Delay 16 Cycles at Dispatch                          | 82 |

|                                                                   |    |

| Table 6-123: Delay 8 Cycles at Dispatch                           | 82 |

| Table 6-124: Data Cache Block Flush                               | 82 |

| Table 6-125: Data Cache Block Store                               | 82 |

| Table 6-126: Data Cache Block Touch                               | 83 |

| Table 6-127: Set Up Streaming Data                                | 83 |

| Table 6-128: Start or Stop Streaming Data                         | 84 |

| Table 6-129: Data Cache Block Touch for Store                     | 84 |

| Table 6-130: Data Cache Block Set to Zero                         | 84 |

| Table 6-131: Enforce In-Order Execution of I/O                    | 84 |

| Table 6-132: Double Absolute Value                                | 85 |

|                                                                   |    |

| Table 6-133: Float Absolute Value                                 | 85 |

| Table 6-134: Convert Doubleword to Double                         | 85 |

| Table 6-135: Convert Double to Doubleword                         | 85 |

| Table 6-136: Convert Double to Doubleword with Round Towards Zero | 86 |

| Table 6-137: Convert Double to Word                               | 86 |

| Table 6-138: Convert Double to Word with Round Towards Zero       | 86 |

| Table 6-139: Double Fused Multiply and Add                        | 86 |

| Table 6-140: Float Fused Multiply and Add                         | 87 |

| Table 6-141: Double Fused Multiply and Subtract                   | 87 |

|                                                                   | 87 |

| Table 6-142: Float Fused Multiply and Subtract                    |    |

| Table 6-143: Double Multiply                                      | 87 |

| Table 6-144: Float Multiply                                       | 88 |

| Table 6-145: Double Negative                                      | 88 |

| Table 6-146: Float Negative                                       | 88 |

| Table 6-147: Double Fused Negative Multiply and Add               | 88 |

| Table 6-148: Float Fused Negative Multiply and Add                | 89 |

| Table 6-149: Double Fused Negative Multiply and Subtract          | 89 |

| Table 6-150: Float Fused Negative Multiply and Subtract           | 89 |

| Table 6-151: Float Reciprocal Estimate                            | 89 |

| Table 6-152: Round to Single Precision                            | 90 |

|                                                                   | 90 |

| Table 6-153: Double Reciprocal Square Root Estimate               |    |

| Table 6-154: Floating-Point Select of Double                      | 90 |

| Table 6-155: Floating-Point Select of Float                       | 90 |

| Table 6-156: Double Square Root                                   | 91 |

| Table 6-157: Float Square Root                                    | 91 |

| Table 6-158: Instruction Cache Block Invalidate                   | 91 |

| Table 6-159: Instruction Sync                                     | 91 |

| Table 6-160: Load Doubleword with Reserved                        | 92 |

| Table 6-161: Load Reversed Doubleword                             | 92 |

| Table 6-162: Load Reversed Halfword                               | 92 |

| Table 6-163: Load Word with Reserved                              | 92 |

| Table 6-164: Load Reversed Word                                   | 93 |

|                                                                   | 93 |

| Table 6-165: Light Weight Sync                                    |    |

| Table 6-166: Move from Floating-Point Status and Control Register | 93 |

| Table 6-167: Move from Special Purpose Register                   | 93 |

| Table 6-168: Move from Time Base                                  | 94 |

| Table 6-169: Reset Bit of FPSCR                                   | 94 |

| Table 6-170: Set Bit of FPSCR                                     | 94 |

| Table 6-171: Set Fields in FPSCR                                  | 94 |

| Table 6-172: Set Field of FPSCR                                   | 95 |

| Table 6-173: Move to Special Purpose Register                     | 95 |

| Table 6-174: Multiply Doubleword, High Part                       | 95 |

| Table 6-175: Multiply Double Unsigned Word, High Part             | 95 |

|                                                                   |    |

| Table 6-176: Multiply Word, High Part                             | 96 |

| Table 6-177: Multiply Unsigned Word, High Part                    | 96 |

| Table 6-178: No Operation                                         | 96 |

| Table 6-179: Rotate Left Doubleword then Clear Left               | 97 |

| Table 6-180: Rotate Left Doubleword then Clear Right              | 98 |

| Table 6-181: Rotate Left Doubleword Immediate then Clear          | 98 |

| Table 6-182: Rotate Left Doubleword Immediate then Clear Left                                                             | 98         |

|---------------------------------------------------------------------------------------------------------------------------|------------|

| Table 6-183: Rotate Left Doubleword Immediate then Clear Right                                                            | 99         |

| Table 6-184: Rotate Left Doubleword Immediate then Mask Insert                                                            | 99         |

| Table 6-185: Rotate Left Word Immediate then Mask Insert                                                                  | 99         |

| Table 6-186: Rotate Left Word Immediate then AND With Mask                                                                | 100        |

| Table 6-187: Rotate Left Word then AND With Mask                                                                          | 100        |

| Table 6-188: Save and Set the FPSCR                                                                                       | 100        |

| Table 6-189: Store Reversed Doubleword                                                                                    | 100        |

| Table 6-190: Store Doubleword Conditional                                                                                 | 101        |

| Table 6-191: Store Reversed Halfword                                                                                      | 101        |

| Table 6-192: Store Reversed Word                                                                                          | 101        |

| Table 6-193: Store Word Conditional                                                                                       | 102        |

| Table 6-194: Sync                                                                                                         | 102        |

| Table 7-195: Stream Control Operators That Have Been Deprecated on the PPU                                                | 104        |

| Table 7-196: Extract Vector Element from Vector                                                                           | 105        |

| Table 7-197: Insert Scalar into Specified Vector Element                                                                  | 106        |

| Table 7-198: Load Vector Left Indexed                                                                                     | 107        |

| Table 7-199: Load Vector Left Indexed Last                                                                                | 108        |

| Table 7-200: Load Vector Right Indexed                                                                                    | 109        |

| Table 7-201: Load Vector Right Indexed Last                                                                               | 110        |

| Table 7-202: Store Vector Left Indexed                                                                                    | 111        |

| Table 7-203: Store Vector Left Indexed Last                                                                               | 112        |

| Table 7-204: Store Vector Right Indexed                                                                                   | 113        |

| Table 7-205: Store Vector Right Indexed Last                                                                              | 114        |

| Table 7-206: Promote Scalar to Vector                                                                                     | 115        |

| Table 7-207: Splat Scalar to Vector                                                                                       | 115        |

| Table 8-208: C Library Header Files                                                                                       | 116        |

| Table 8-209: Fastest Minimum-Width Integer Types                                                                          | 117        |

| Table 8-210: Vector Formats                                                                                               | 118        |

| Table 8-211: C++ Library Header Files                                                                                     | 119        |

| Table 8-212: New and Traditional C++ Library Header Files                                                                 | 120        |

| Table 9-213: Values for Floating-Point Type Properties                                                                    | 122        |

| Table 9-214: Rounding Mode for Two Bits of FLT_ROUNDS                                                                     | 123        |

| Table 9-215: Macros for Double Precision Rounding Modes Table 9-216: Macros for Single Precision Floating Point Eventions | 123<br>124 |

| Table 9-216: Macros for Single Precision Floating-Point Exceptions                                                        |            |

| Table 9-217: Macros for Double Precision Floating-Point Exceptions                                                        | 124        |

| Table 9-218: Floating-Point Constants Table 10, 219: Integer Vector Types                                                 | 125        |

| Table 10-219: Integer Vector Types Table 10-229: Floating Point Vector Types                                              | 130<br>130 |

| Table 10-220: Floating-Point Vector Types Table 10-221: Valid Types for Specified Unary Operators                         |            |

| Table 10-221: Valid Types for Specified Unary Operators  Table 10-222: Valid Types for Specified Binary Operators         | 130<br>131 |

| Table 10-222: Valid Types for Specified Billary Operators  Table 10-223: Valid Types for Specified Relational Operators   | 131        |

| Table 10-220. Valid Types for Openited Netational Operators                                                               | 131        |

|                                                                                                                           |            |

# **List of Figures**

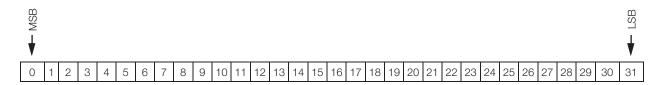

| Figure 1-1: Big-Endian Byte/Element Ordering for Vector Types | xxi |

|---------------------------------------------------------------|-----|

| Figure 2-2: Shuffle Pattern                                   | 31  |

xiii

#### **About This Document**

This document describes language extension specifications that allow software developers to access hardware features that are not easily accessible from a high level language, such as C or C++, in order to obtain the best performance from a Synergistic Processor Unit (SPU) and a PowerPC<sup>®</sup> Processor Unit (PPU) of the Cell Broadband Engine™. This document also includes function specifications to facilitate communication between SPUs and PPU, and it lists a minimal set of standard library functions that must be provided as part of a standard SPU programming environment.

#### **Audience**

This document is intended for system and application programmers who want to write SPU and PPU programs for a CBEA-compliant processor.

#### **Version History**

This section describes significant changes made to each version of this document.

| Version Number & Date        | Changes                                                                                                                                                                     |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v. 2.5<br>February 27, 2008  | Resize several intrinsic table fields so that vector unsigned long long parameter types are not inadvertently truncated to vector unsigned long.                            |

| v. 2.5<br>September 14, 2007 | Corrected miscellaneous documentation errors (TWG_RFC00102-1: CORRECTION NOTICE).                                                                                           |

|                              | Added six new PPU intrinsics to simplify streaming data prefetch (TWG_RFC00103-0 as amended by TWG_RFC00103-1).                                                             |

|                              | Described special behaviors for some of the missing classification macros (TWG_RFC00104-0).                                                                                 |

|                              | Changed the return/argument types of several PPU intrinsics (TWG_RFC00105-0).                                                                                               |

|                              | Changed the descriptive names of the SPU rotate and shift intrinsics (TWG_RFC00106-2).                                                                                      |

|                              | Changed the descriptive names of several intrinsics (TWG_RFC00107-2: CORRECTION NOTICE).                                                                                    |

|                              | Added a section describing the MFC tag mananger (TWG_RFC00109-2).                                                                                                           |

|                              | Eliminated unnecessary spaces from several headings (TWG_RFC00111-0: CORRECTION NOTICE).                                                                                    |

|                              | Specified the SPU "fastest minimum-width integer" typedefs in a way that conforms with the implementations for both spu-gcc and spuxlc (TWG_RFC00117-0).                    |

|                              | Clarified the mapping of intrinsics between SPU and VMX (TWG_RFC00118-1).                                                                                                   |

|                              | Corrected the implementation specification of the mfc_hl2ea function so that it matches the implementation in spu_mfcio.h. (TWG_RFC00119-0: CORRECTION NOTICE).             |

|                              | Made miscellaneous editorial changes.                                                                                                                                       |

| v. 2.4                       | Added support for enhanced double precision SPU instructions (TWG_RFC00071-0).                                                                                              |

| March 8, 2007                | Specified use of vector data types with standard C/C++ operators (TWG_RFC00082-1).                                                                                          |

|                              | Made it explicit that the vector keyword n the SPU is the same as the vector keyword on the PPU (TWG_RFC00096-0).                                                           |

|                              | Provided a predefined macro for use by compilers that are targeted to a processor that supports the SPU's optional enhanced double precision instructions (TWG_RFC00097-0). |

| Version Number & Date      | Changes                                                                                                                                                                                                                                                 |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | Attached "volatile" with dmalist arguments in intrinsics (TWG_RFC00100-0).                                                                                                                                                                              |