# IBM

# Cell Broadband Engine Programming Handbook

Version 1.1

© Copyright International Business Machines Corporation, Sony Computer Entertainment Incorporated, Toshiba Corporation 2006, 2007.

All Rights Reserved Printed in the United States of America April 2007

The following are trademarks of International Business Machines Corporation in the United States or other countries, or both.

IBM eServer ibm.com PowerPC

IBM Logo PowerPC Architecture

Cell Broadband Engine is a trademark of Sony Computer Entertainment, Inc.

Java and all Java-based trademarks are trademarks of Sun Microsystems, Inc. in the United States, other countries, or both.

Intel is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

UNIX is a registered trademark of The Open Group in the United States and other countries.

Linux is a trademark of Linus Torvalds in the United States, other countries, or both.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems and Technology Group 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at **ibm.com**®

The IBM Semiconductor solutions home page can be found at **ibm.com**/chips

Version 1.1 April 24, 2007

# **Contents**

| List of Figures                                    | 19   |

|----------------------------------------------------|------|

| List of Tables                                     | 23   |

| Preface                                            | 29   |

| Related Publications                               | . 29 |

| Conventions and Notation                           |      |

| Referencing Registers, Fields, and Bit Ranges      |      |

| Terminology                                        |      |

| Reserved Regions of Memory and Registers           |      |

| Revision Log                                       | 33   |

| 1. Overview of the Cell Broadband Engine Processor | 37   |

| 1.1 Background                                     | . 38 |

| 1.1.1 Motivation                                   |      |

| 1.1.2 Power, Memory, and Frequency                 |      |

| 1.1.3 Scope of this Handbook                       |      |

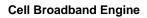

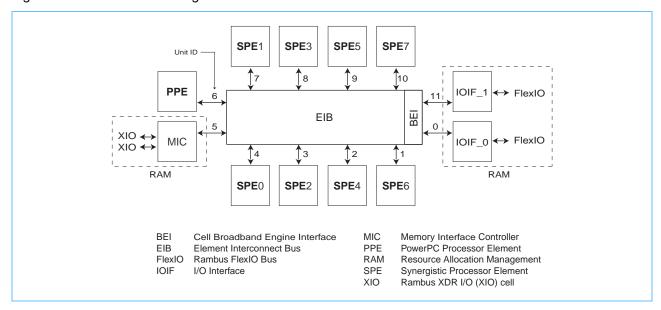

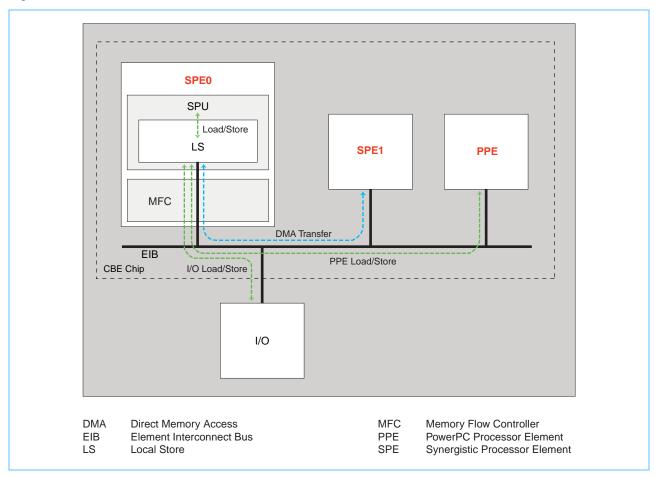

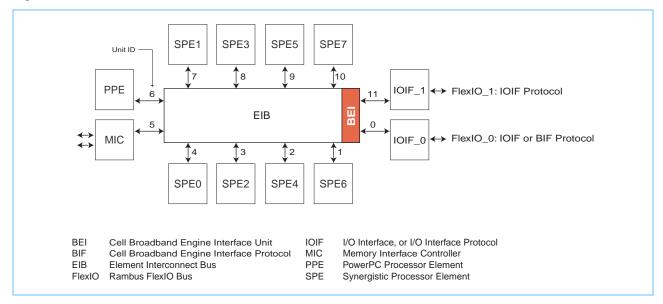

| 1.2 Hardware Environment                           |      |

| 1.2.1 The Processor Elements                       |      |

| 1.2.2 Element Interconnect Bus                     |      |

| 1.2.3 Memory Interface Controller                  |      |

| 1.2.4 Cell Broadband Engine Interface Unit         |      |

| 1.3 Programming Environment                        |      |

| 1.3.1 Instruction Sets                             |      |

| 1.3.2 Storage Domains and Interfaces               |      |

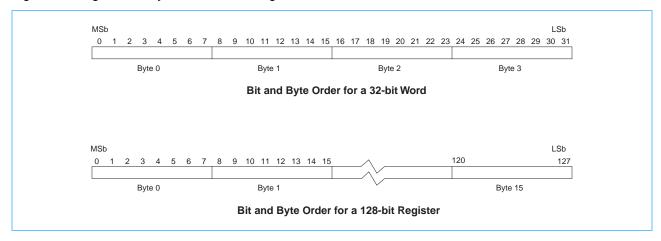

| 1.3.3 Byte Ordering and Bit Numbering              |      |

| 1.3.4 Runtime Environment                          | . 40 |

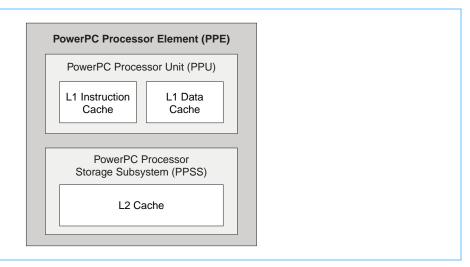

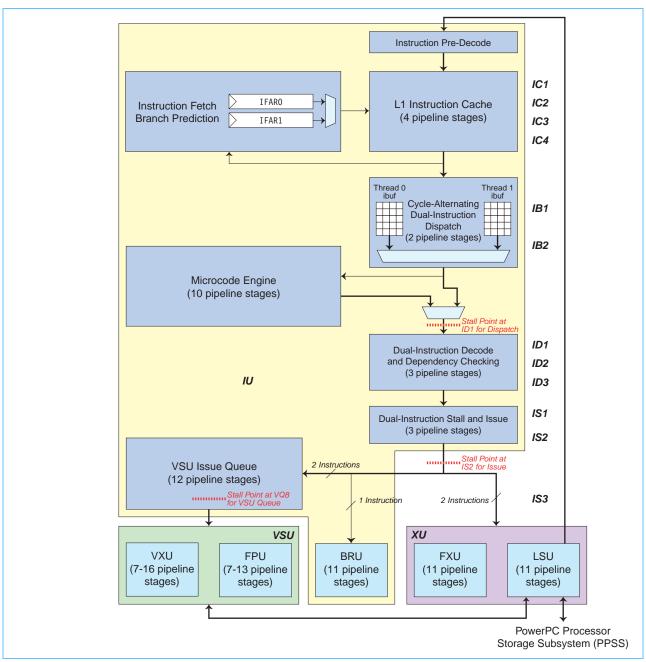

| 2. PowerPC Processor Element                       | _    |

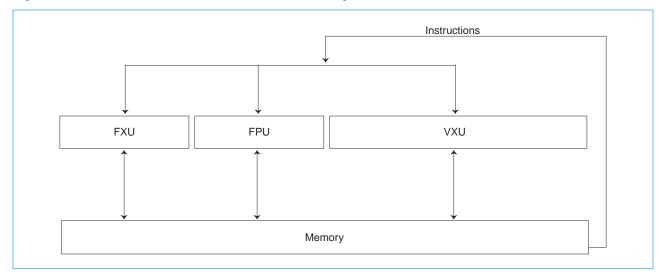

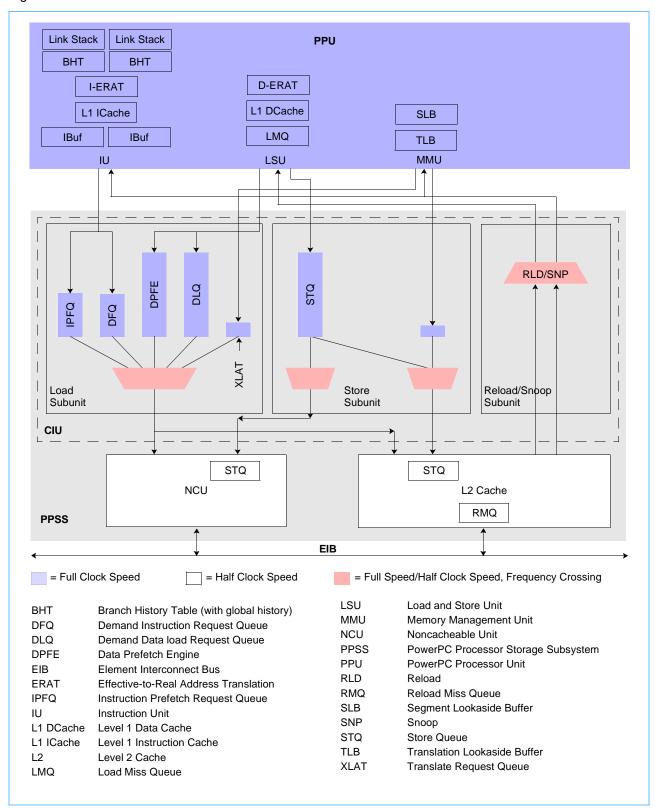

| 2.1 PowerPC Processor Unit                         |      |

| 2.2 PowerPC Processor Storage Subsystem            |      |

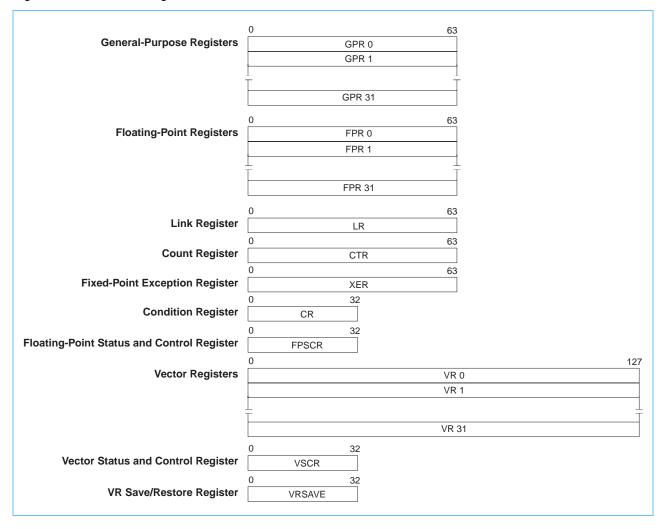

| 2.3 PPE Registers                                  |      |

| 2.4 PowerPC Instructions                           |      |

| 2.4.1 Data Types                                   |      |

| 2.4.2 Addressing Modes                             |      |

| 2.4.3 Instructions                                 |      |

| 2.5 Vector/SIMD Multimedia Extension Instructions  |      |

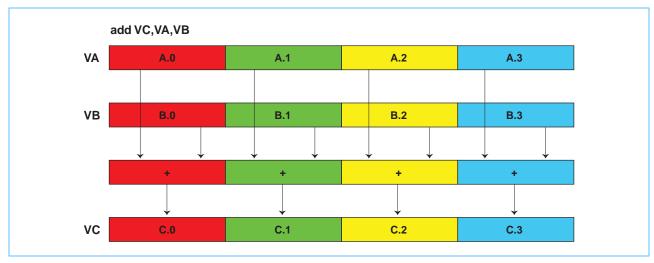

| 2.5.1 SIMD Vectorization                           |      |

| 2.5.2 Data Types                                   |      |

| 2.5.3 Addressing Modes                             |      |

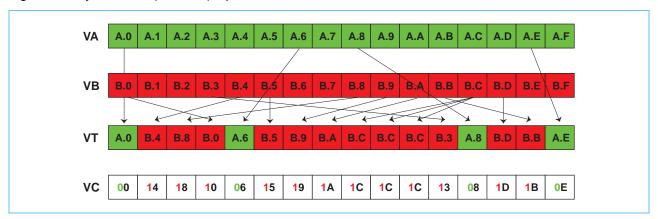

| 2.5.4 Instruction Types                            |      |

| 2.5.5 Instructions                                 |      |

| 2.5.6 Graphics Rounding Mode                       | . 60 |

|                                         | C++ Language Intrinsics |                |

|-----------------------------------------|-------------------------|----------------|

| • • • • • • • • • • • • • • • • • • • • |                         |                |

|                                         |                         |                |

| 2.6.3 Intrinsics                        |                         | 61             |

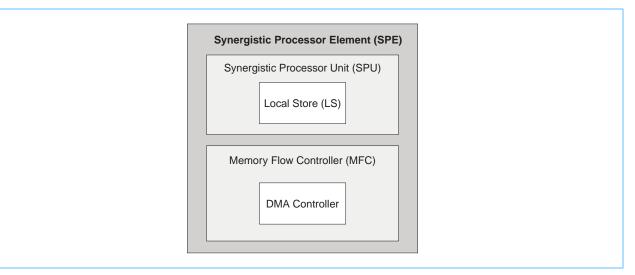

| 3. Synergistic Processor Elements       |                         | 63             |

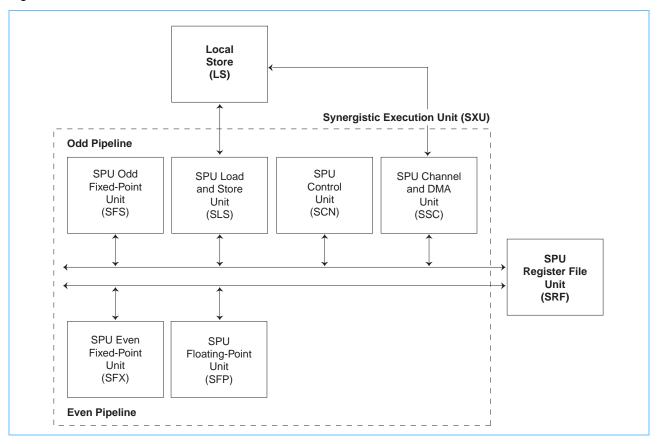

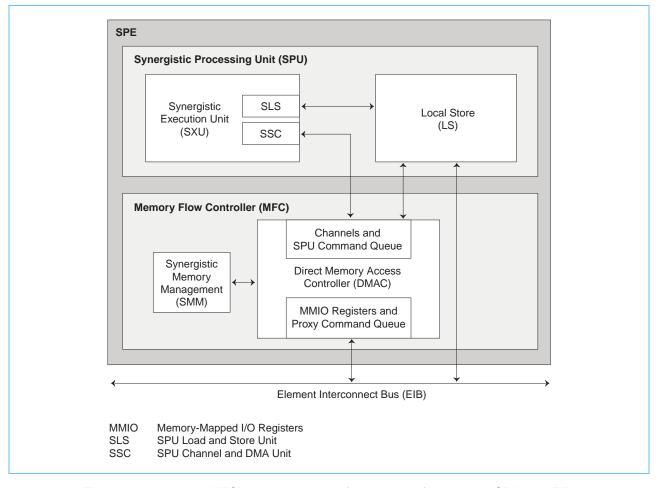

| 3.1 Synergistic Processor Unit          |                         | 63             |

| 3.1.1 Local Store                       |                         | 64             |

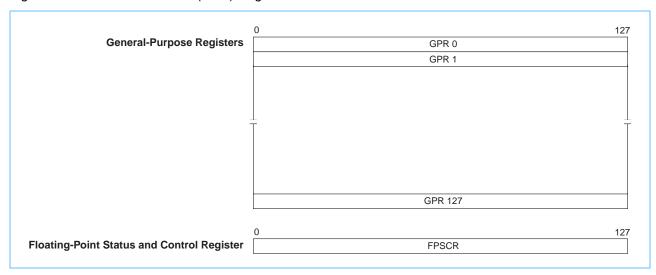

| 3.1.2 Register File                     |                         | 67             |

| 3.1.3 Execution Units                   |                         | 68             |

| 3.1.4 Floating-Point Support            |                         | 68             |

| 3.2 Memory Flow Controller              |                         | 70             |

| 3.2.1 Channels                          |                         | 72             |

|                                         |                         |                |

|                                         | Queues                  |                |

|                                         |                         |                |

| , , , , , , , , , , , , , , , , , , , , | t Unit                  |                |

| 3.3 SPU Instruction Set                 |                         | 74             |

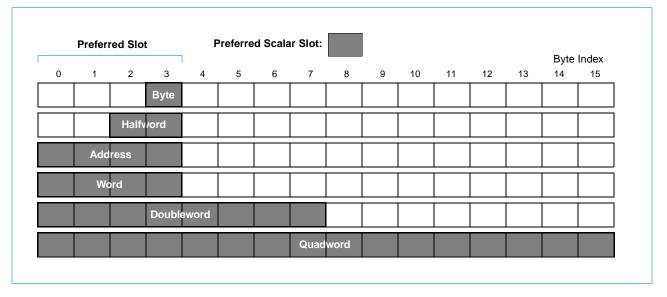

| 3.3.1 Data Types                        |                         | 74             |

| 3.3.2 Instructions                      |                         | 75             |

| 3.4 SPU C/C++ Language Intrinsics       |                         | 75             |

| 3.4.1 Vector Data Types                 |                         | 76             |

| 3.4.2 Vector Literals                   |                         | 76             |

| 3.4.3 Intrinsics                        |                         | 76             |

|                                         |                         |                |

|                                         |                         |                |

|                                         |                         |                |

| 4.1 Introduction                        |                         | 77             |

| 4.1 Introduction                        |                         | 77<br>78       |

| 4.1 Introduction                        |                         | 77<br>78<br>79 |

| 4.1 Introduction                        |                         |                |

| 4.1 Introduction                        |                         |                |

| 4.1 Introduction                        | ation                   |                |

| 4.1 Introduction                        | ationde                 |                |

| 4.1 Introduction                        | ationde                 |                |

| 4.1 Introduction                        | ationde                 |                |

| 4.1 Introduction                        | ationdet Unit           |                |

| 4.1 Introduction                        | ationde                 |                |

| 4.1 Introduction                        | ationdet Unit           |                |

| 4.1 Introduction                        | de                      |                |

|    | 5.1.2 Allocated Regions of Memory                    |     |

|----|------------------------------------------------------|-----|

|    | 5.1.3 Reserved Regions of Memory                     |     |

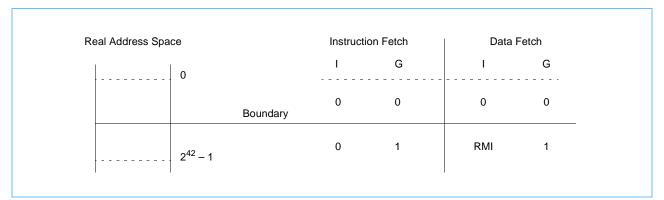

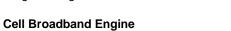

|    | 5.1.4 The Guarded Attribute                          | 124 |

|    | 5.2 PPE Memory Map                                   | 124 |

|    | 5.2.1 PPE Memory-Mapped Registers                    |     |

|    | 5.2.2 Predefined Real-Address Locations              | 125 |

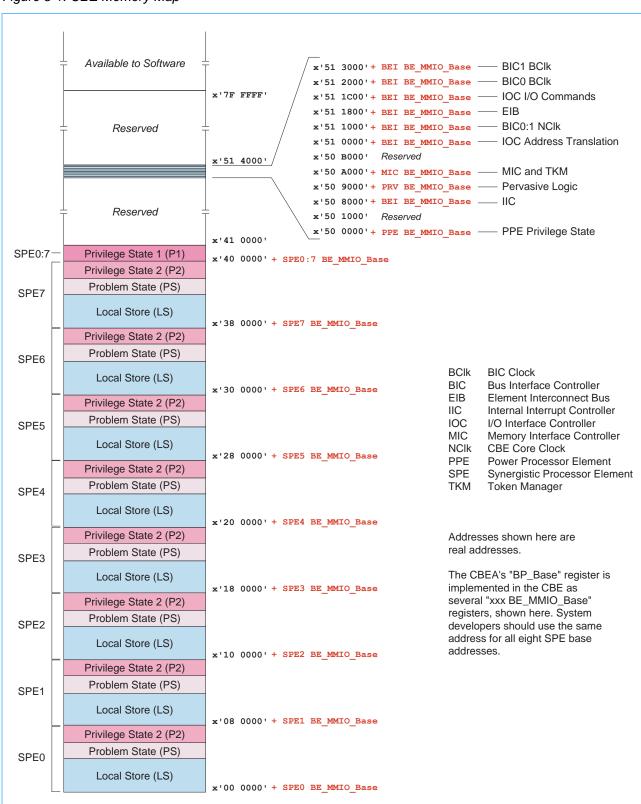

|    | 5.3 SPE Memory Map                                   |     |

|    | 5.3.1 SPE Local-Store Memory Map                     |     |

|    | 5.3.2 SPE Memory-Mapped Registers                    |     |

|    | 5.4 BEI Memory-Mapped Registers                      |     |

|    | 5.4.1 I/O                                            |     |

|    | 5.4.1 I/O                                            | 129 |

| _  | Nacha Managanani                                     | 404 |

| о. | Cache Management                                     |     |

|    | 6.1 PPE Caches                                       |     |

|    | 6.1.1 Configuration                                  |     |

|    | 6.1.2 Overview of PPE Cache                          |     |

|    | 6.1.3 L1 Caches                                      |     |

|    | 6.1.4 Branch History Table and Link Stack            | 139 |

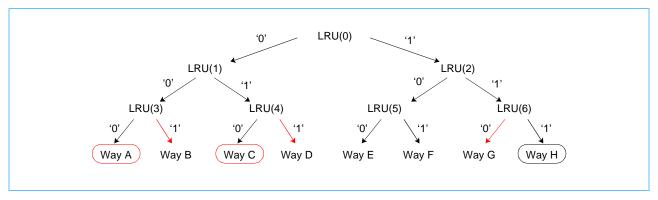

|    | 6.1.5 L2 Cache                                       | 139 |

|    | 6.1.6 Instructions for Managing the L1 and L2 Caches | 144 |

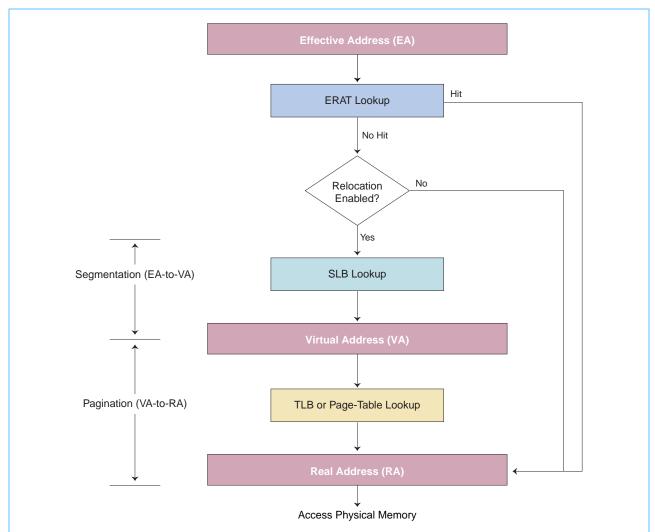

|    | 6.1.7 Effective-to-Real-Address Translation Arrays   | 148 |

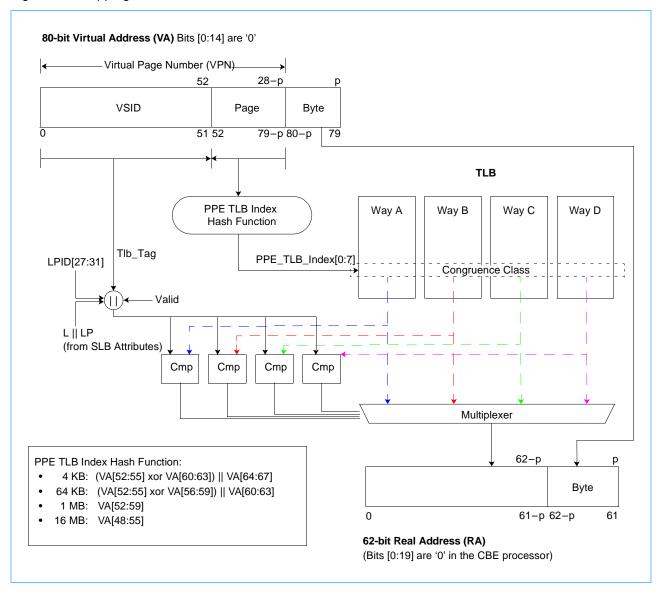

|    | 6.1.8 Translation Lookaside Buffer                   | 148 |

|    | 6.1.9 Instruction-Prefetch Queue Management          | 148 |

|    | 6.1.10 Load Subunit Management                       |     |

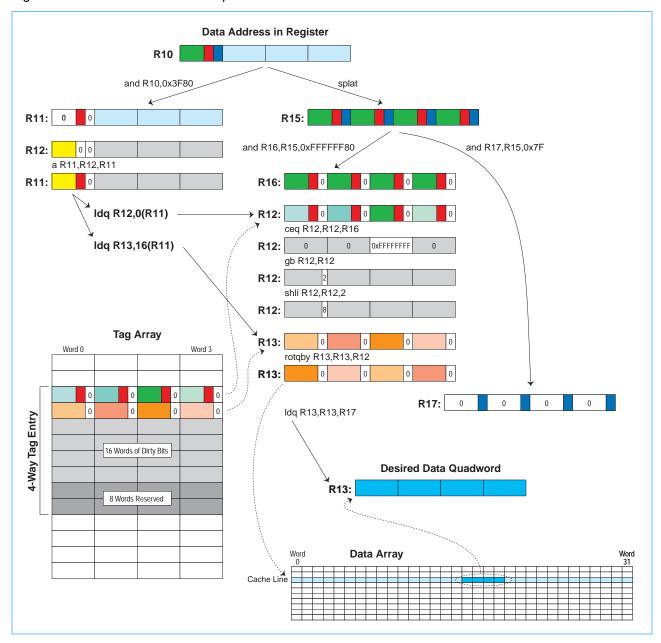

|    | 6.2 SPE Caches                                       |     |

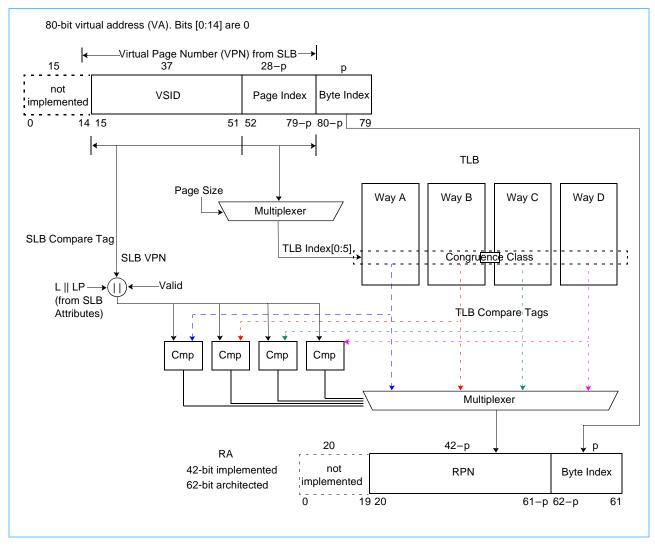

|    | 6.2.1 Translation Lookaside Buffer                   |     |

|    | 6.2.2 Atomic Unit and Cache                          |     |

|    | 6.3 Replacement Management Tables                    |     |

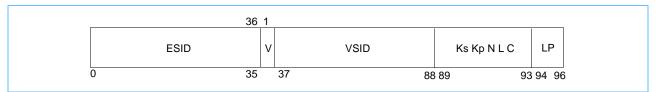

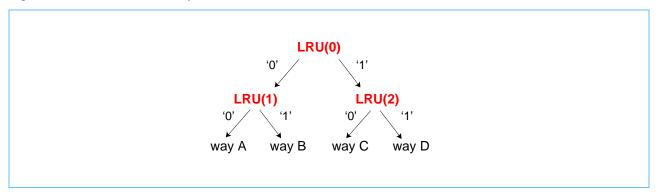

|    | 6.3.1 PPE TLB Replacement Management Table           |     |

|    | 6.3.2 PPE L2 Replacement Management Table            |     |

|    | 6.3.3 SPE TLB Replacement Management Table           |     |

|    | · · · · · · · · · · · · · · · · · · ·                |     |

|    | 6.4 I/O Address-Translation Caches                   | 157 |

| _  |                                                      | 450 |

| 1. | O Architecture                                       |     |

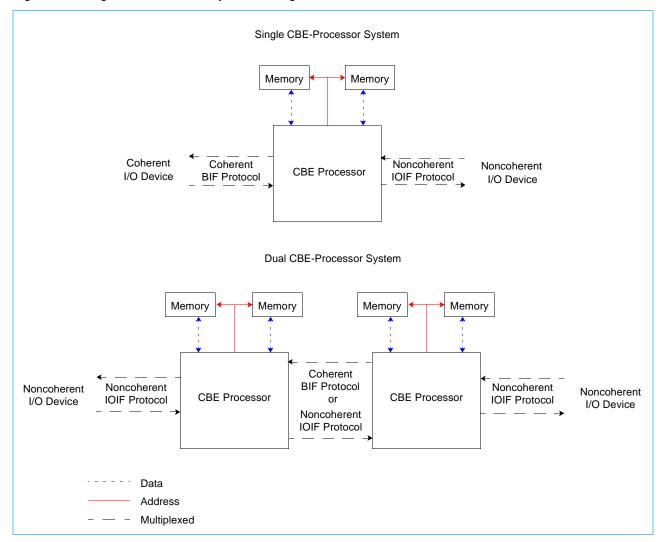

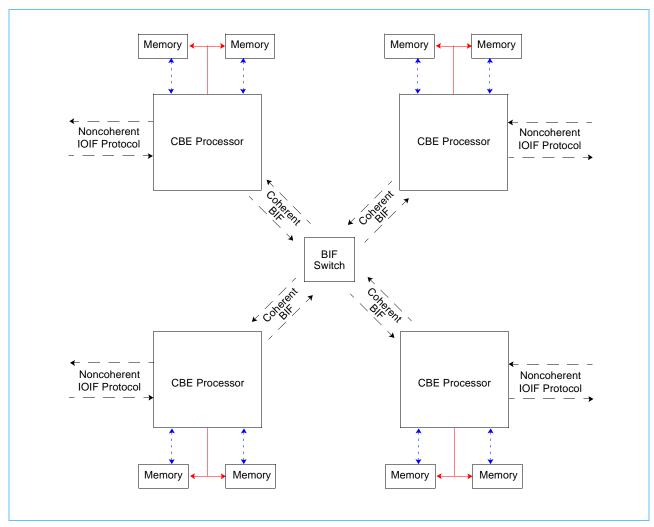

|    | 7.1 Overview                                         |     |

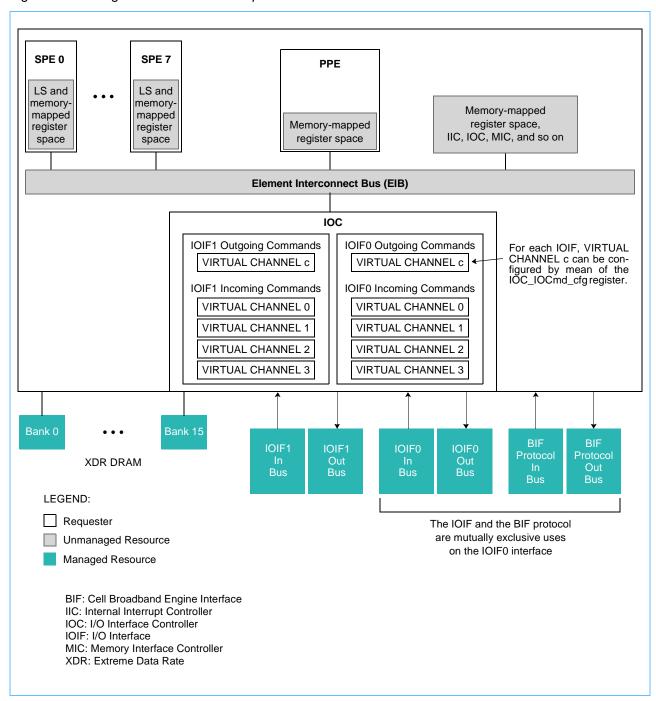

|    | 7.1.1 I/O Interfaces                                 |     |

|    | 7.1.2 System Configurations                          |     |

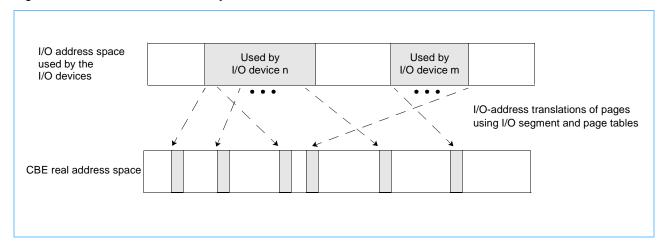

|    | 7.1.3 I/O Addressing                                 | 162 |

|    | 7.2 Data and Access Types                            | 163 |

|    | 7.2.1 Data Lengths and Alignments                    | 163 |

|    | 7.2.2 Atomic Accesses                                |     |

|    | 7.3 Registers and Data Structures                    | 164 |

|    | 7.3.1 IOCmd Configuration Register                   |     |

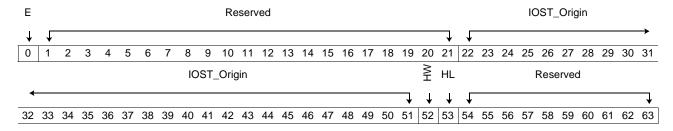

|    | 7.3.2 I/O Segment Table Origin Register              |     |

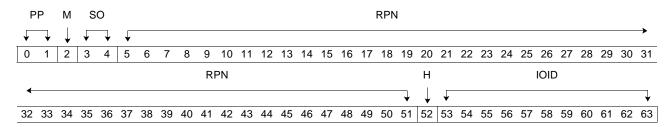

|    | 7.3.3 I/O Segment Table                              |     |

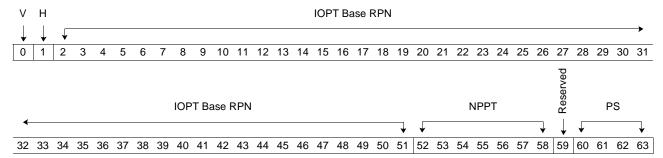

|    | 7.3.4 I/O Page Table                                 |     |

|    | 7.3.5 IOC Base Address Registers                     |     |

|    | 7.3.6 I/O Exception Status Register                  |     |

|    |                                                      |     |

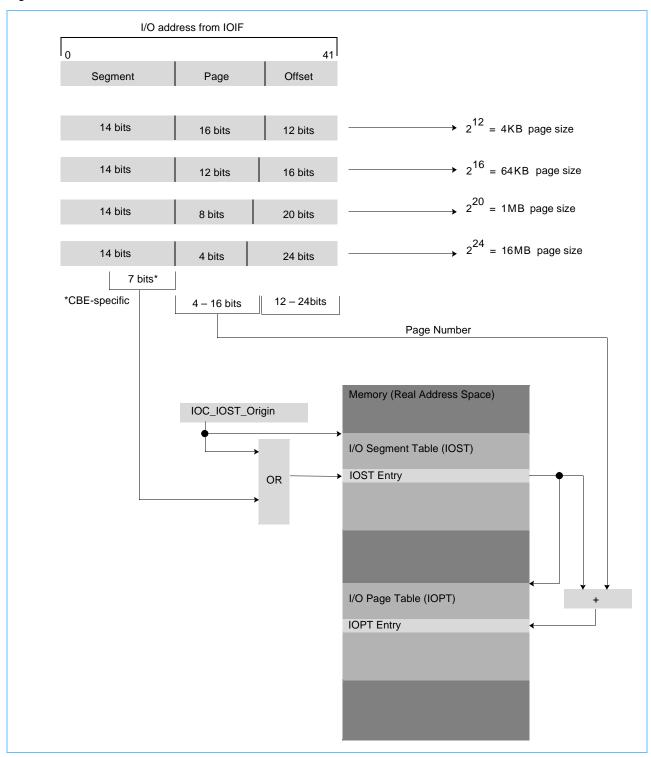

| 7.4 I/O Address Translation                                    | 174 |

|----------------------------------------------------------------|-----|

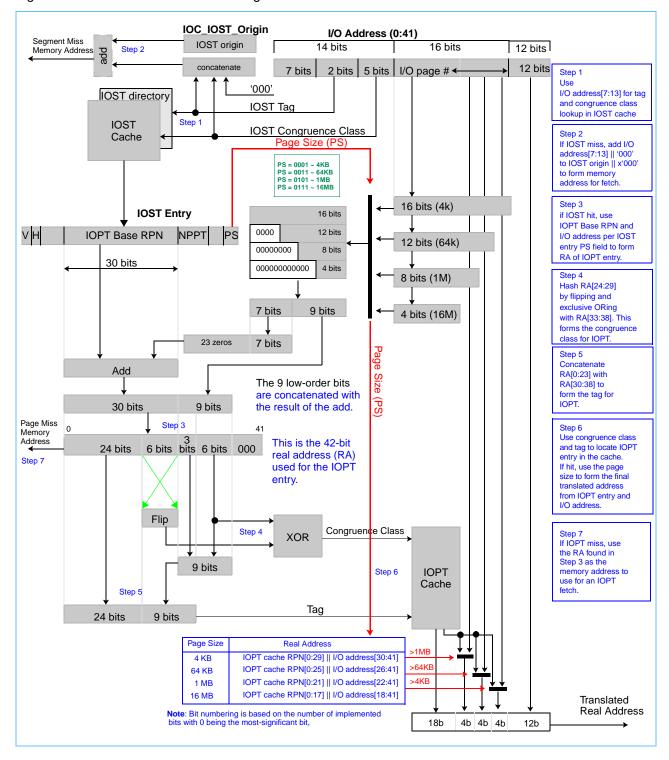

| 7.4.1 Translation Overview                                     | 174 |

| 7.4.2 Translation Steps                                        | 177 |

| 7.5 I/O Exceptions                                             | 179 |

| 7.5.1 I/O Exception Causes                                     |     |

| 7.5.2 I/O Exception Status Register                            | 180 |

| 7.5.3 I/O Exception Mask Register                              |     |

| 7.5.4 I/O-Exception Response                                   |     |

| 7.6 I/O Address-Translation Caches                             |     |

| 7.6.1 IOST Cache                                               |     |

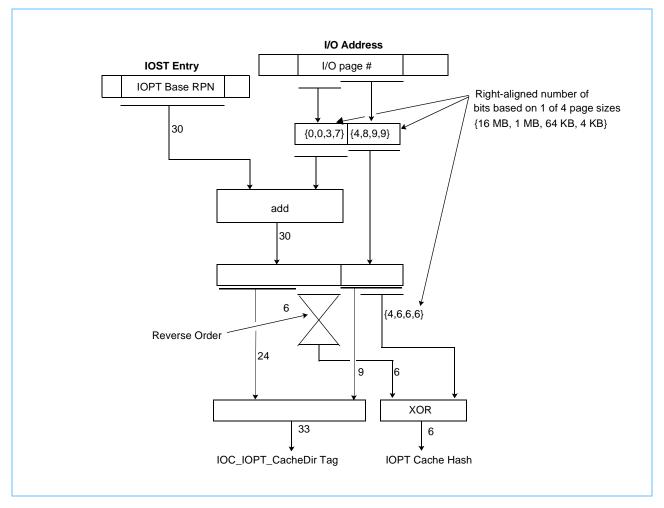

| 7.6.2 IOPT Cache                                               |     |

| 7.7 I/O Storage Model                                          |     |

| 7.7.1 Memory Coherence                                         |     |

| 7.7.2 Storage-Access Ordering                                  |     |

| 7.7.3 I/O Accesses to Other I/O Units through an IOIF          |     |

| 7.7.4 Examples                                                 | 194 |

| 8. Resource Allocation Management                              | 201 |

| 8.1 Introduction                                               | 201 |

| 8.2 Requesters                                                 |     |

| 8.2.1 PPE and SPEs                                             |     |

| 8.2.2 I/O                                                      | 204 |

| 8.3 Managed Resources                                          |     |

| 8.4 Tokens                                                     |     |

| 8.4.1 Tokens Required for Single-CBE-Processor Systems         |     |

| 8.4.2 Operations Requiring No Token                            |     |

| 8.4.3 Tokens Required for Multi-CBE-Processor Systems          |     |

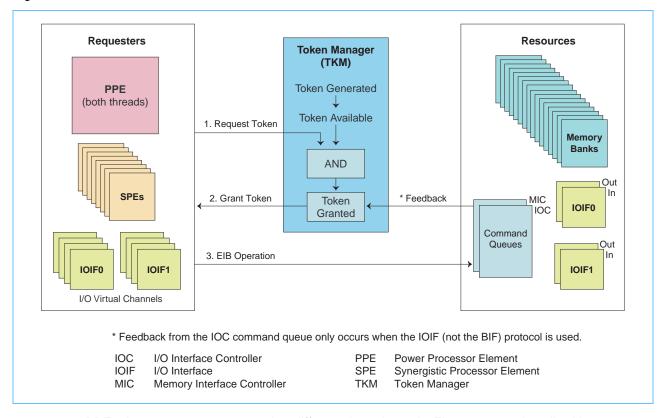

| 8.5 Token Manager                                              |     |

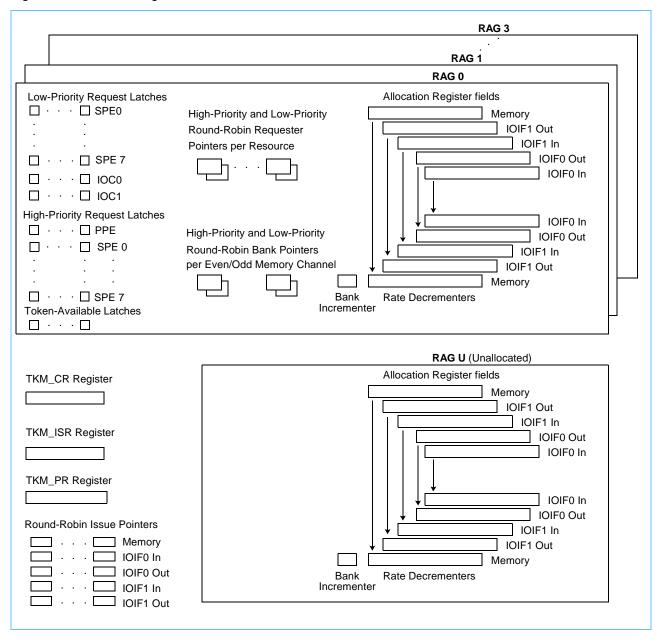

| 8.5.1 Request Tracking                                         |     |

| 8.5.2 Token Granting                                           |     |

| 8.5.3 Unallocated RAG                                          |     |

| 8.5.4 High-Priority Token Requests                             |     |

| 8.5.5 Memory Tokens<br>8.5.6 I/O Tokens                        |     |

| 8.5.7 Unused Tokens                                            |     |

| 8.5.8 Memory Banks, IOIF Allocation Rates, and Unused Tokens   |     |

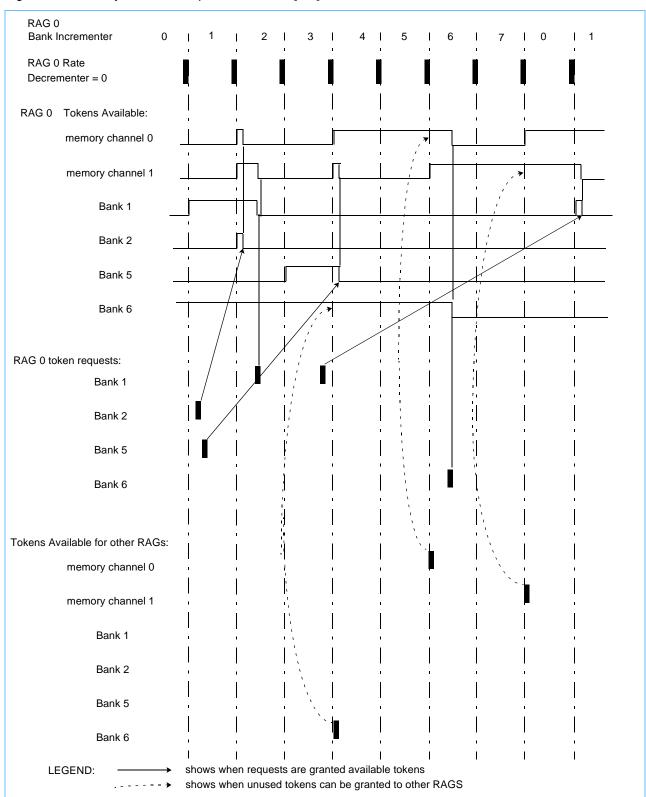

| 8.5.9 Token Request and Grant Example                          |     |

| 8.5.10 Allocation Percentages                                  |     |

| 8.5.11 Efficient Determination of TKM Priority Register Values |     |

| 8.5.12 Feedback from Resources to Token Manager                |     |

| 8.6 Configuration of PPE, SPEs, MIC, and IOC                   |     |

| 8.6.1 Configuration Register Summary                           |     |

| 8.6.2 SPE Address-Range Checking                               |     |

| 8.7 Changing Resource-Management Registers with MMIO Stores    |     |

| 8.7.1 Changes to the RAID                                      |     |

| 8.7.2 Changing a Requester's Token-Request Enable              |     |

| 8.7.3 Changing a Requester's Address Map                       |     |

| 8.7.4 Changing a Requester's Use of Multiple Tokens per Access | 234 |

|                                                                |     |

|            | 8.7.5 Changing Feedback to the TKM                         | 224 |

|------------|------------------------------------------------------------|-----|

|            | 8.7.6 Changing TKM Registers                               |     |

|            | 8.8 Latency Between Token Requests and Token Grants        |     |

|            | 8.9 Hypervisor Interfaces                                  |     |

|            | 0.5 Hypervisor interfaces                                  | 200 |

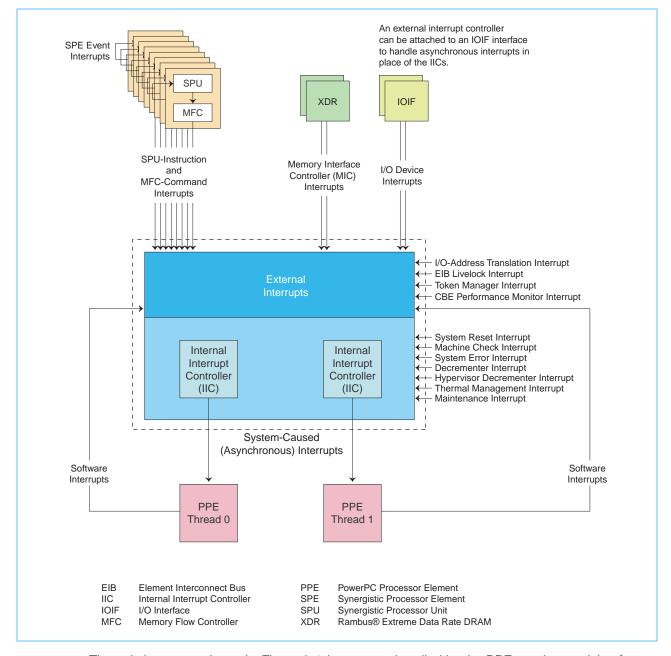

| a          | PPE Interrupts                                             | 237 |

| <b>J</b> . | 9.1 Introduction                                           |     |

|            |                                                            |     |

|            | 9.2 Summary of Interrupt Architecture                      |     |

|            | 9.3 Interrupt Registers                                    |     |

|            | 9.4 Interrupt Handling                                     |     |

|            | 9.5 Interrupt Vectors and Definitions                      |     |

|            | 9.5.1 System Reset Interrupt (Selectable or x'0000000100') |     |

|            | 9.5.2 Machine Check Interrupt (x'000000200')               |     |

|            | 9.5.3 Data Storage Interrupt (x'000000300')                |     |

|            | 9.5.4 Data Segment Interrupt (x'000000380')                |     |

|            | 9.5.5 Instruction Storage Interrupt (x'000000400')         |     |

|            | 9.5.6 Instruction Segment Interrupt (x'0000000480')        |     |

|            | 9.5.7 External Interrupt (x'000000500')                    |     |

|            | 9.5.8 Alignment Interrupt (x'000000600')                   |     |

|            | 9.5.9 Program Interrupt (x'000000700')                     |     |

|            | 9.5.10 Floating-Point Unavailable Interrupt (x'000000800') |     |

|            | 9.5.11 Decrementer Interrupt (x'000000900')                |     |

|            | 9.5.12 Hypervisor Decrementer Interrupt (x'000000980')     |     |

|            | 9.5.13 System Call Interrupt (x'000000C00')                |     |

|            | 9.5.14 Trace Interrupt (x'000000D00')                      |     |

|            | 9.5.15 VXU Unavailable Interrupt (x'000000F20')            |     |

|            | 9.5.16 System Error Interrupt (x'000001200')               |     |

|            | 9.5.17 Maintenance Interrupt (x'000001600')                |     |

|            | 9.5.18 Thermal Management Interrupt (x'0000001800')        |     |

|            | 9.6 Direct External Interrupts                             |     |

|            | 9.6.1 Interrupt Presentation                               |     |

|            | 9.6.2 IIC Interrupt Registers                              |     |

|            | 9.6.3 SPU and MFC Interrupts                               |     |

|            | 9.6.4 Other External Interrupts                            |     |

|            | 9.7 Mediated External Interrupts                           |     |

|            | 9.7.1 Mediated External Interrupt Architecture             |     |

|            | 9.7.2 Mediated External Interrupt Implementation           |     |

|            | 9.8 SPU and MFC Interrupts Routed to the PPE               |     |

|            | 9.8.1 Interrupt Types and Classes                          |     |

|            | 9.8.2 Interrupt Registers                                  |     |

|            | 9.8.3 Interrupt Definitions                                |     |

|            | 9.8.4 Handling SPU and MFC Interrupts                      |     |

|            | 9.9 Thread Targets for Interrupts                          |     |

|            | 9.10 Interrupt Priorities                                  |     |

|            | 9.11 Interrupt Latencies                                   |     |

|            | 9.12 Machine State Register Settings Due to Interrupts     | 291 |

|            | 9.13 Interrupts and Hypervisor                             | 293 |

|            | 9.14 Interrupts and Multithreading                         | 293 |

|            |                                                            |     |

|    | 9.15 Checkstop                                                                         |     |

|----|----------------------------------------------------------------------------------------|-----|

|    | 9.16 Use of an External Interrupt Controller                                           |     |

|    | 9.17 Relationship Between CBE and PowerPC Interrupts                                   | 294 |

| 10 | . PPE Multithreading                                                                   | 295 |

|    | 10.1 Multithreading Guidelines                                                         |     |

|    | 10.2 Thread Resources                                                                  |     |

|    | 10.2.1 Registers                                                                       |     |

|    | 10.2.2 Arrays, Queues, and Other Structures                                            |     |

|    | 10.2.3 Pipeline Sharing and Support for Multithreading                                 |     |

|    | 10.3 Thread States                                                                     |     |

|    | 10.3.1 Privilege States                                                                |     |

|    | 10.3.2 Suspended or Enabled State                                                      |     |

|    | 10.3.3 Blocked or Stalled State                                                        |     |

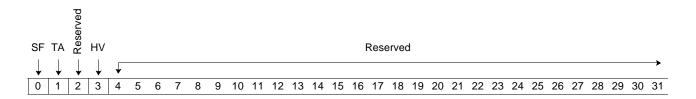

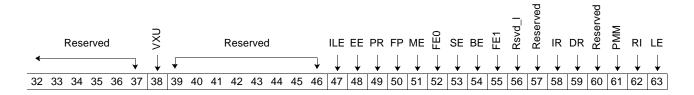

|    | 10.4 Thread Control and Status Registers                                               | 302 |

|    | 10.4.1 Machine State Register (MSR)                                                    |     |

|    | 10.4.2 Hardware Implementation Register 0 (HID0)                                       |     |

|    | 10.4.3 Logical Partition Control Register (LPCR)                                       | 305 |

|    | 10.4.4 Control Register (CTRL)                                                         |     |

|    | 10.4.5 Thread Status Register Local and Remote (TSRL and TSRR)                         |     |

|    | 10.4.6 Thread Switch Control Register (TSCR)                                           |     |

|    | 10.4.7 Thread Switch Time-Out Register (TTR)                                           |     |

|    | 10.5 Thread Priority                                                                   |     |

|    | 10.5.1 Thread-Priority Combinations                                                    |     |

|    | 10.5.2 Choosing Useful Thread Priorities                                               |     |

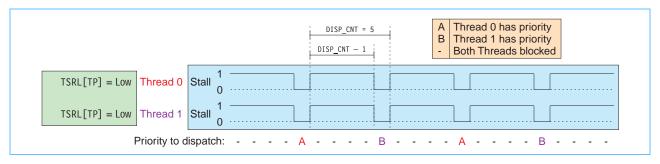

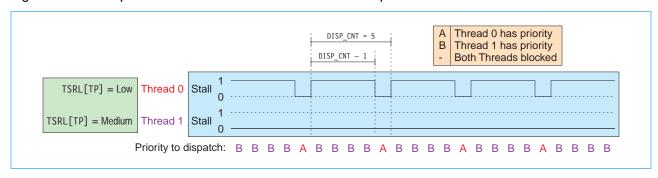

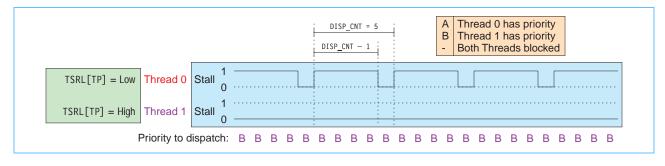

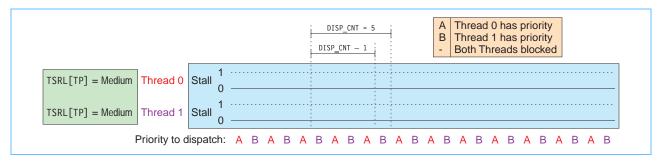

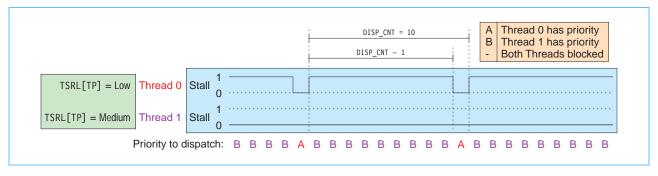

|    | 10.5.3 Examples of Priority Combinations on Instruction Scheduling                     |     |

|    | 10.6 Thread Control and Configuration                                                  |     |

|    | 10.6.1 Resuming and Suspending Threads                                                 |     |

|    | 10.6.2 Setting the Instruction-Dispatch Policy: Thread Priority and Temporary Stalling |     |

|    | 10.6.3 Preventing Starvation: Forward-Progress Monitoring                              |     |

|    |                                                                                        |     |

|    | 10.7 Pipeline Events and Instruction Dispatch                                          |     |

|    | 10.7.2 Pipeline Events that Stall Instruction Dispatch                                 |     |

|    | 10.8 Suspending and Resuming Threads                                                   |     |

|    | 10.8.1 Suspending a Thread                                                             |     |

|    | 10.8.2 Resuming a Thread                                                               |     |

|    | 10.8.3 Exception and Interrupt Interactions With a Suspended Thread                    |     |

|    | 10.8.4 Thread Targets and Behavior for Interrupts                                      |     |

|    |                                                                                        |     |

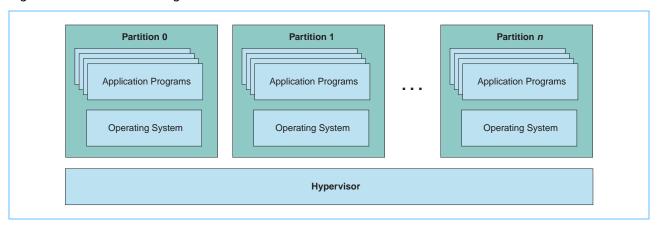

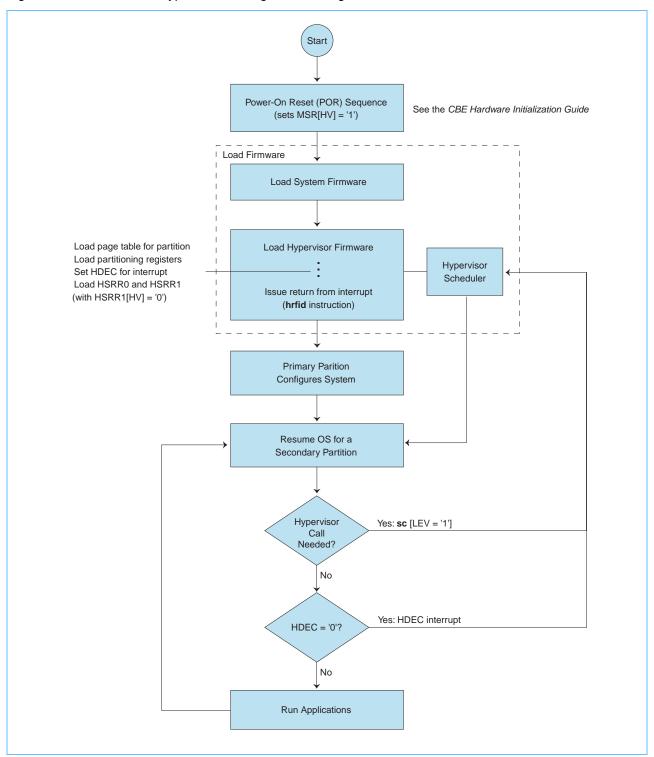

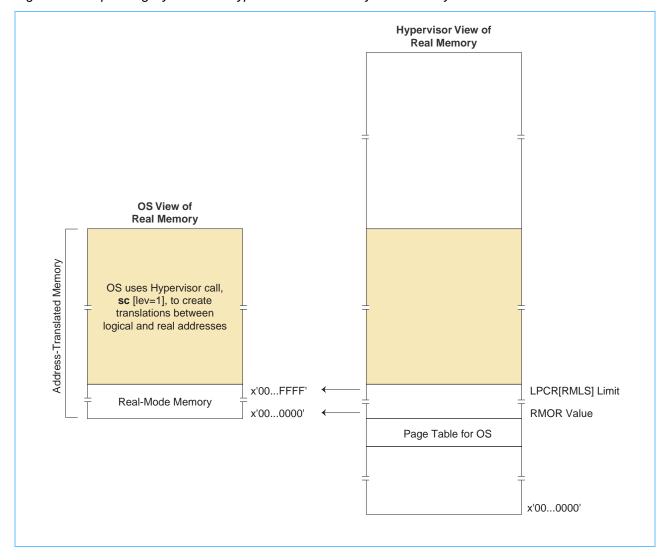

| 11 | . Logical Partitions and a Hypervisor                                                  |     |

|    | 11.1 Introduction                                                                      |     |

|    | 11.1.1 The Hypervisor and the Operating Systems                                        |     |

|    | 11.1.2 Partitioning Resources                                                          |     |

|    | 11.1.3 An Example Flowchart                                                            |     |

|    | 11.2 PPE Logical-Partitioning Facilities                                               |     |

|    | 11.2.1 Enabling Hypervisor State                                                       |     |

|    | 11.2.2 Hypervisor-State Registers                                                      | 331 |

|    | 11.2.3 Controlling Real Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|    | 11.2.4 Controlling Interrupts and Environment                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

|    | 11.3 SPE Logical-Partitioning Facilities                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

|    | 11.3.1 Access Privilege                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |

|    | 11.3.2 Memory-Management Facilities                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |

|    | 11.3.3 Controlling Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 344                                                                       |

|    | 11.3.4 Other SPE Management Facilities                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                           |

|    | 11.4 I/O-Address Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

|    | 11.4.1 IOC Memory Management Units                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

|    | 11.4.2 I/O Segment and Page Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

|    | 11.5 Resource Allocation Management                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |

|    | 11.5.1 Combining Logical Partitions with Resource Allocation                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

|    | , ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |

|    | 11.6 Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

|    | 11.6.2 Thread State Suspension and Resumption                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |

|    | 11.7 Fault Isolation                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                           |

|    | 11.8 Code Sample                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                           |

|    | 11.8.2 C Functions for PowerPC 64-bit ELF Hypervisor Call                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                           |

|    | 11.0.2 Of unctions for Fowerr O of bit EEF Trypervisor Out                                                                                                                                                                                                                                                                                                                                                                                                                        | 040                                                                       |

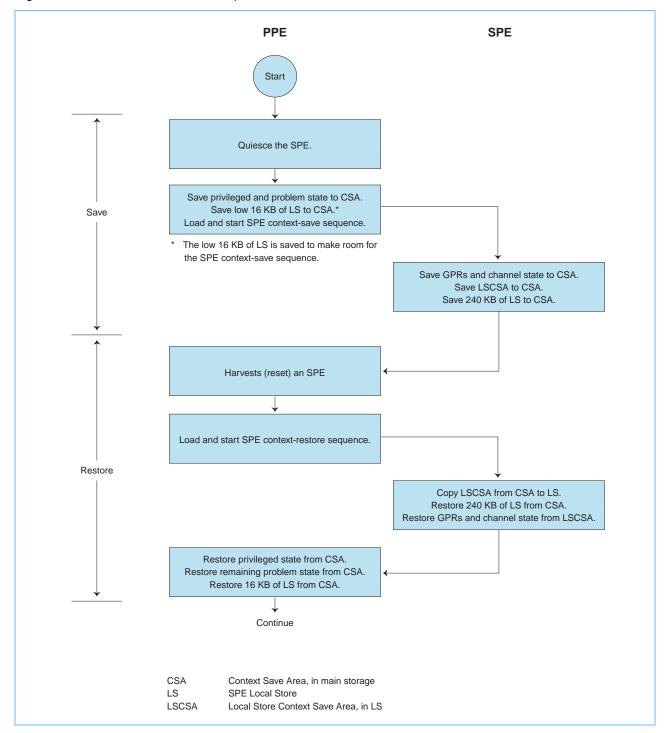

| 12 | . SPE Context Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 351                                                                       |

| _  | 12.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                           |

|    | 12.2 Data Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

|    | 12.2.1 Local Store Context Save Area                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                           |

|    | 12.2.2 Context Save Area                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

|    | 12.3 Overview of SPE Context-Switch Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                           |

|    | 12.3.1 Save SPE Context                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |

|    | 12.3.2 Restore SPE Context                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                           |

|    | 12.4 Implementation Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                | 356                                                                       |

|    | 12.4.1 Locking                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |

|    | 12.4.2 Watchdog Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 050                                                                       |

|    | 12.4.2 Watchdog Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 356                                                                       |

|    | 12.4.3 Waiting for Events                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                           |

|    | 12.4.3 Waiting for Events                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 356<br>356                                                                |

|    | 12.4.3 Waiting for Events                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 356<br>356<br>356                                                         |

|    | 12.4.3 Waiting for Events  12.4.4 PPE's SPU Channel Access Facility  12.4.5 SPE Interrupts  12.4.6 Suspending the MFC DMA Queue                                                                                                                                                                                                                                                                                                                                                   | 356<br>356<br>356<br>357                                                  |

|    | 12.4.3 Waiting for Events  12.4.4 PPE's SPU Channel Access Facility  12.4.5 SPE Interrupts  12.4.6 Suspending the MFC DMA Queue  12.4.7 SPE Context-Save Sequence and Context-Restore Sequence Code                                                                                                                                                                                                                                                                               | 356<br>356<br>356<br>357<br>357                                           |

|    | 12.4.3 Waiting for Events  12.4.4 PPE's SPU Channel Access Facility  12.4.5 SPE Interrupts  12.4.6 Suspending the MFC DMA Queue  12.4.7 SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.8 SPE Parameter Passing                                                                                                                                                                                                                                                 | 356<br>356<br>356<br>357<br>357<br>357                                    |

|    | 12.4.3 Waiting for Events  12.4.4 PPE's SPU Channel Access Facility  12.4.5 SPE Interrupts  12.4.6 Suspending the MFC DMA Queue  12.4.7 SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.8 SPE Parameter Passing  12.4.9 Storage for SPE Context-Save Sequence and Context-Restore Sequence Code                                                                                                                                                                 | 356<br>356<br>356<br>357<br>357<br>357<br>357                             |

|    | 12.4.3 Waiting for Events  12.4.4 PPE's SPU Channel Access Facility  12.4.5 SPE Interrupts  12.4.6 Suspending the MFC DMA Queue  12.4.7 SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.8 SPE Parameter Passing  12.4.9 Storage for SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.10 Harvesting an SPE                                                                                                                                      | 356<br>356<br>357<br>357<br>357<br>357<br>358                             |

|    | 12.4.3 Waiting for Events  12.4.4 PPE's SPU Channel Access Facility  12.4.5 SPE Interrupts  12.4.6 Suspending the MFC DMA Queue  12.4.7 SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.8 SPE Parameter Passing  12.4.9 Storage for SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.10 Harvesting an SPE  12.4.11 Scheduling                                                                                                                  | 356<br>356<br>357<br>357<br>357<br>357<br>358<br>358                      |

|    | 12.4.3 Waiting for Events  12.4.4 PPE's SPU Channel Access Facility  12.4.5 SPE Interrupts  12.4.6 Suspending the MFC DMA Queue  12.4.7 SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.8 SPE Parameter Passing  12.4.9 Storage for SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.10 Harvesting an SPE  12.4.11 Scheduling  12.4.12 Light-Weight SPE Context Save                                                                           | 356<br>356<br>357<br>357<br>357<br>357<br>358<br>358<br>358               |

|    | 12.4.3 Waiting for Events  12.4.4 PPE's SPU Channel Access Facility  12.4.5 SPE Interrupts  12.4.6 Suspending the MFC DMA Queue  12.4.7 SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.8 SPE Parameter Passing  12.4.9 Storage for SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.10 Harvesting an SPE  12.4.11 Scheduling  12.4.12 Light-Weight SPE Context Save                                                                           | 356<br>356<br>357<br>357<br>357<br>358<br>358<br>358<br>359               |

|    | 12.4.3 Waiting for Events  12.4.4 PPE's SPU Channel Access Facility  12.4.5 SPE Interrupts  12.4.6 Suspending the MFC DMA Queue  12.4.7 SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.8 SPE Parameter Passing  12.4.9 Storage for SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.10 Harvesting an SPE  12.4.11 Scheduling  12.4.12 Light-Weight SPE Context Save  12.5 Detailed Steps for SPE Context Switch  12.5.1 Context-Save Sequence | 356<br>356<br>357<br>357<br>357<br>357<br>358<br>358<br>358<br>359<br>359 |

|    | 12.4.3 Waiting for Events  12.4.4 PPE's SPU Channel Access Facility  12.4.5 SPE Interrupts  12.4.6 Suspending the MFC DMA Queue  12.4.7 SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.8 SPE Parameter Passing  12.4.9 Storage for SPE Context-Save Sequence and Context-Restore Sequence Code  12.4.10 Harvesting an SPE  12.4.11 Scheduling  12.4.12 Light-Weight SPE Context Save                                                                           | 356<br>356<br>357<br>357<br>357<br>358<br>358<br>358<br>359<br>359<br>365 |

| 13. | . Time Base and Decrementers                                                     |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | 13.1 Introduction                                                                |     |

|     | 13.2 Time-Base Facility                                                          |     |

|     | 13.2.1 Clock Domains                                                             |     |

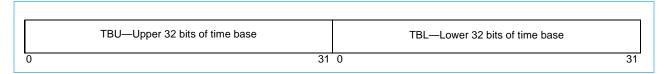

|     | 13.2.2 Time-Base Registers                                                       |     |

|     | 13.2.3 Time-Base Frequency                                                       |     |

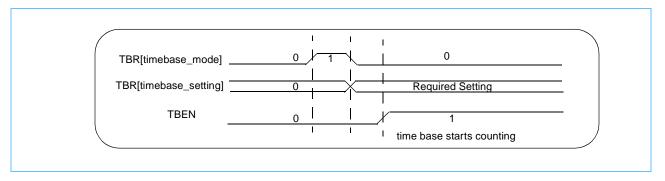

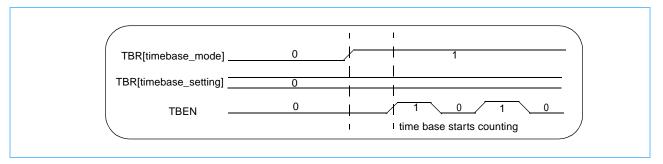

|     | 13.2.4 Time-Base Sync Mode Controls                                              |     |

|     | 13.2.5 Reading and Writing the TB Register                                       |     |

|     | 13.2.6 Computing Time-of-Day                                                     |     |

|     | 13.3 Decrementers                                                                |     |

|     | 13.3.1 PPE Decrementers                                                          |     |

|     | 13.3.2 SPE Decrementers                                                          |     |

|     | 13.3.3 Using an SPU Decrementer to Monitor SPU Code Performance                  | 385 |

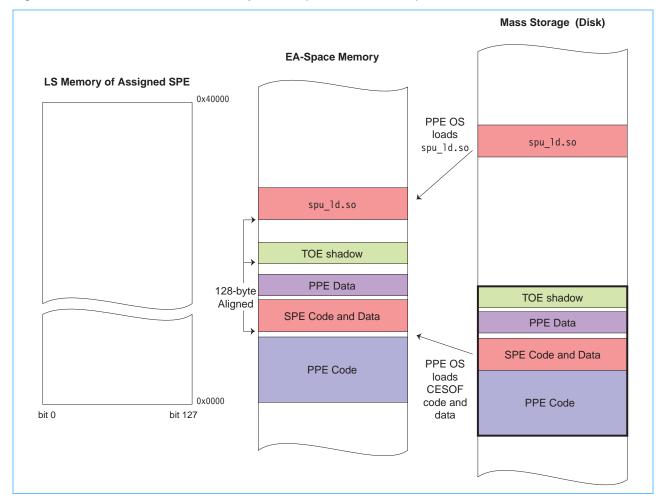

| 14. | . Objects, Executables, and SPE Loading                                          | 391 |

|     | 14.1 Introduction                                                                | 391 |

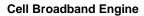

|     | 14.2 ELF Overview and Extensions                                                 | 392 |

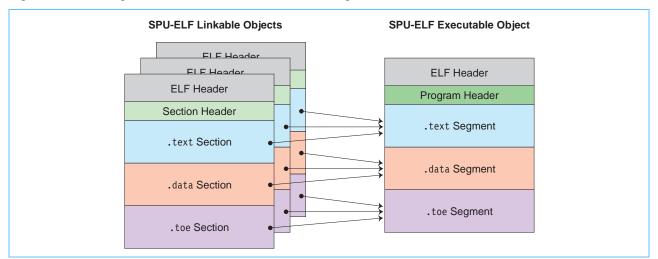

|     | 14.2.1 Overview                                                                  | 392 |

|     | 14.2.2 SPE-ELF Extensions                                                        | 393 |

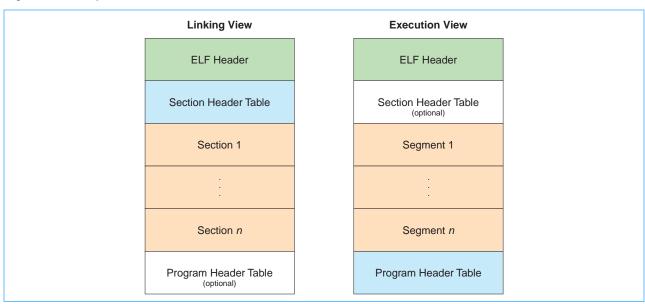

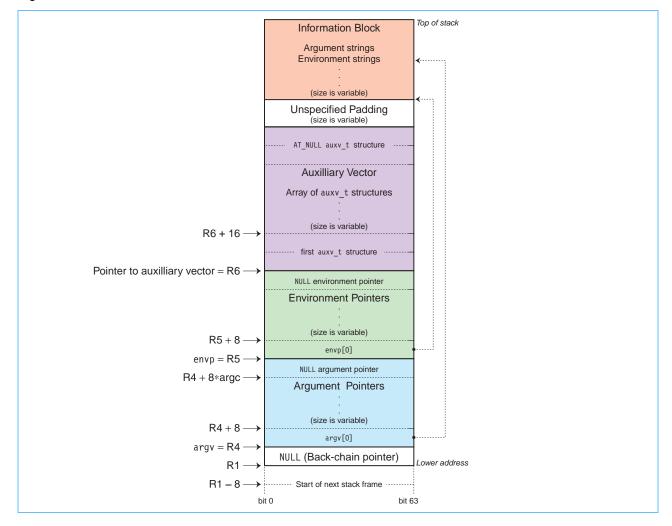

|     | 14.3 Runtime Initializations and Requirements                                    | 395 |

|     | 14.3.1 PPE Initial Machine State                                                 |     |

|     | 14.3.2 SPE Initial Machine State for Linux                                       |     |

|     | 14.4 Linker Requirements                                                         | 401 |

|     | 14.4.1 SPE Linker Requirements                                                   |     |

|     | 14.4.2 PPE Linker Requirements                                                   |     |

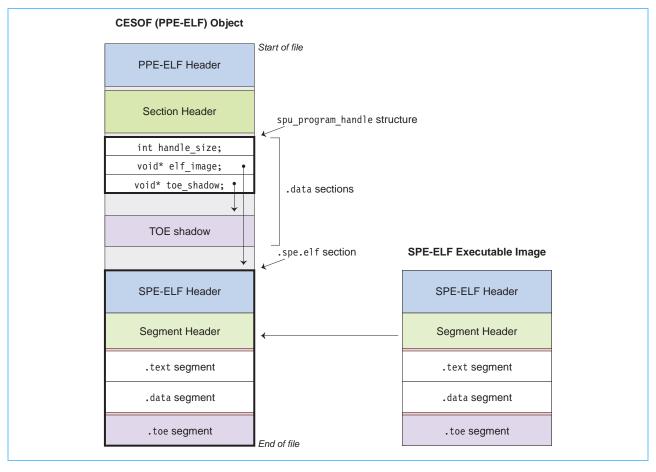

|     | 14.5 The CESOF Format                                                            |     |

|     | 14.5.1 CESOF Overview                                                            |     |

|     | 14.5.2 CESOF Use Convention of ELF                                               |     |

|     | 14.5.3 Embedding an SPE-ELF Executable in a PPE-ELF Object: The .spu.elf Section |     |

|     | 14.5.4 The spe program handle Data Structure                                     |     |

|     | 14.5.5 The TOE: Accessing Symbol Values Defined in EA Space                      |     |

|     | 14.5.6 Future Software Tool Chain Enhancements for CESOF                         | 411 |

|     | 14.6 SPE Runtime Loader                                                          | 412 |

|     | 14.6.1 Runtime Loader Overview                                                   |     |

|     | 14.6.2 SPE Runtime Loader Requirements                                           | 413 |

|     | 14.6.3 Example SPE Runtime Loader Framework Definition                           | 415 |

|     | 14.7 SPE Execution Environment                                                   | 421 |

|     | 14.7.1 Signal Types for the SPE Stop-and-Signal Instruction                      | 421 |

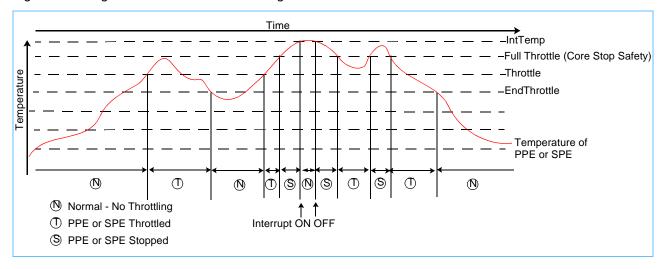

| 15  | . Power and Thermal Management                                                   | 123 |

| 10. | 15.1 Power Management                                                            |     |

|     | 15.1.1 CBE Slow State                                                            |     |

|     |                                                                                  |     |

|     | 15.1.2 PPE Pause (0) State                                                       |     |

|     | 15.1.4 MFC Pause State                                                           |     |

|     |                                                                                  |     |

|     | 15.2 Thermal Management                                                          |     |

|     | 15.2.2 Configuration-Ring Settings                                               |     |

|     | 15.2.3 Thermal Registers                                                         |     |

|     | 10.2.0 Thomas Negloters                                                          | ∠3  |

|    | 15.2.4 Thermal Sensor Status Registers                                    | 429 |

|----|---------------------------------------------------------------------------|-----|

|    | 15.2.5 Thermal Sensor Interrupt Registers                                 |     |

|    | 15.2.6 Dynamic Thermal-Management Registers                               |     |

| 16 | . Performance Monitoring                                                  | 437 |

|    | 16.1 How It Works                                                         | 438 |

|    | 16.2 Events (Signals)                                                     | 438 |

|    | 16.3 Performance Counters                                                 | 438 |

|    | 16.4 Trace Array                                                          | 439 |

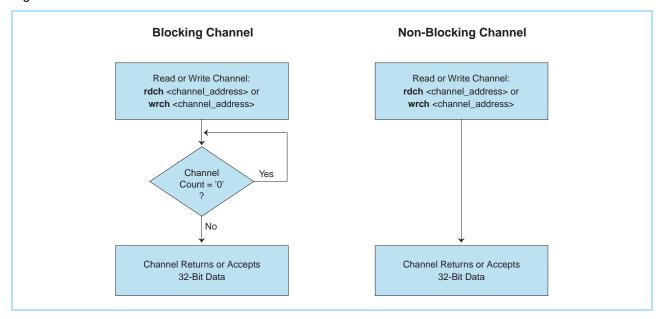

| 17 | . SPE Channel and Related MMIO Interface                                  | 441 |

|    | 17.1 Introduction                                                         | 441 |

|    | 17.1.1 An SPE's Use of its Own Channels                                   | 441 |

|    | 17.1.2 Access to Channel Functions by the PPE and other SPEs              | 442 |

|    | 17.1.3 Channel Characteristics                                            |     |

|    | 17.1.4 Channel Summary                                                    |     |

|    | 17.1.5 Channel Instructions                                               |     |

|    | 17.1.6 Channel Capacity and Blocking                                      |     |

|    | 17.2 SPU Event-Management Channels                                        |     |

|    | 17.3 SPU Signal-Notification Channels                                     |     |

|    | 17.4 SPU Decrementer                                                      |     |

|    | 17.4.1 SPU Write Decrementer Channel                                      |     |

|    | 17.4.2 SPU Read Decrementer Channel                                       |     |

|    | 17.5 MFC Write Multisource Synchronization Request Channel                |     |

|    | 17.6 SPU Read Machine Status Channel                                      |     |

|    | 17.7 SPU Write State Save-and-Restore Channel                             |     |

|    | 17.8 SPU Read State Save-and-Restore Channel                              | 451 |

|    | 17.9 MFC Command Parameter Channels                                       |     |

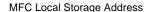

|    | 17.9.1 MFC Local Storage Address Channel                                  |     |

|    | 17.9.2 MFC Effective Address High Channel                                 |     |

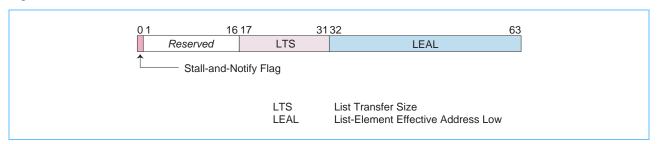

|    | 17.9.3 MFC Effective Address Low or List Address Channel                  |     |

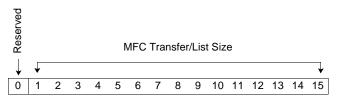

|    | 17.9.4 MFC Transfer Size or List Size Channel                             |     |

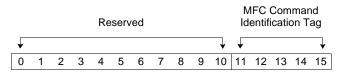

|    | 17.9.5 MFC Command Tag Identification Channel                             |     |

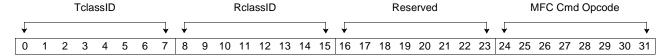

|    | 17.9.6 MFC Class ID and MFC Command Opcode Channel                        |     |

|    | 17.10 MFC Tag-Group Management Channels                                   |     |

|    | 17.10.1 MFC Write Tag-Group Query Mask Channel                            |     |

|    | 17.10.2 MFC Read Tag-Group Query Mask Channel                             |     |

|    | 17.10.3 MFC Write Tag Status Opdate Request Charmer                       |     |

|    | 17.10.5 MFC Read List Stall-and-Notify Tag Status Channel                 |     |

|    | 17.10.6 MFC Write List Stall-and-Notify Tag Acknowledgment Channel        |     |

|    | 17.11 MFC Read Atomic Command Status Channel                              |     |

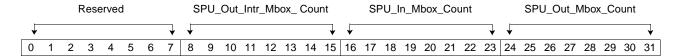

|    | 17.12 SPU Mailbox Channels                                                |     |

| 19 | s. SPE Events                                                             | 165 |

| 10 |                                                                           |     |

|    | 18.1 Introduction                                                         |     |

|    | 18.2 Events and Event-Management Channels                                 |     |

|    | 10.2.1 Event Conditions and bit Delinitions for Event-Management Channels | 400 |

| 18.2.2 Pending Event Register (Internal, SPE-Hidden)                                   | 467 |

|----------------------------------------------------------------------------------------|-----|

| 18.2.3 SPU Read Event Status                                                           | 468 |

| 18.2.4 SPU Write Event Mask                                                            | 469 |

| 18.2.5 SPU Write Event Acknowledgment                                                  | 469 |

| 18.2.6 SPU Read Event Mask                                                             | 470 |

| 18.3 SPU Interrupt Facility                                                            | 470 |

| 18.4 Interrupt Address Save-and-Restore Channels                                       | 471 |

| 18.4.1 SPU Read State Save-and-Restore                                                 | 471 |

| 18.4.2 SPU Write State Save-and-Restore                                                | 471 |

| 18.4.3 Nested Interrupts Using SPU Write State Save-and-Restore                        | 471 |

| 18.5 Event-Handling Protocols                                                          | 472 |

| 18.5.1 Synchronous Event Handling Using Polling or Stalling                            | 472 |

| 18.5.2 Asynchronous Event Handling Using Interrupts                                    | 473 |

| 18.5.3 Protecting Critical Sections from Interruption                                  | 474 |

| 18.6 Event-Specific Handling Guidelines                                                | 475 |

| 18.6.1 Protocol with Multiple Events Enabled                                           |     |

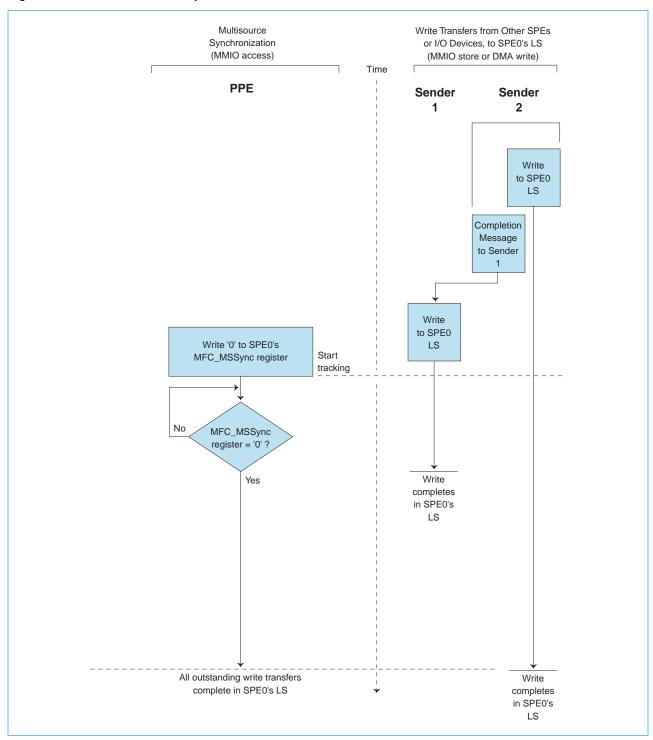

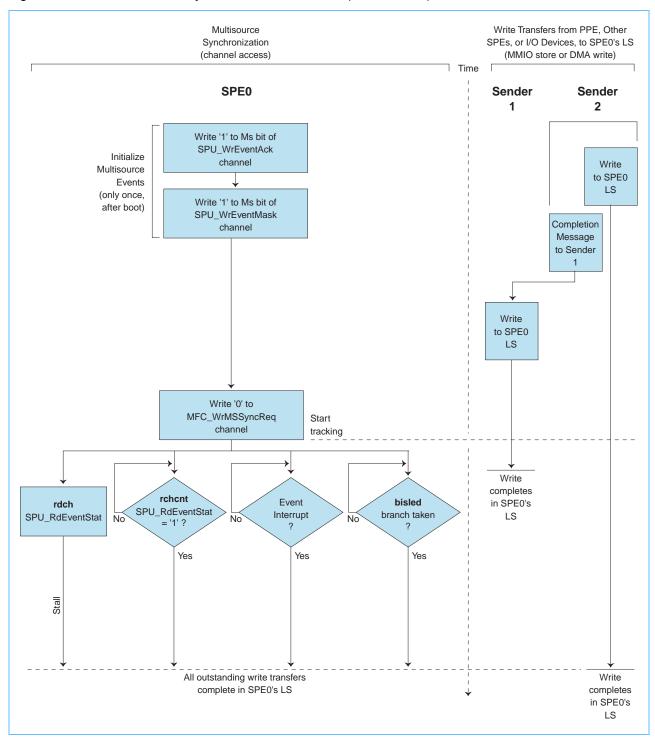

| 18.6.2 Procedure for Handling the Multisource Synchronization Event                    | 477 |

| 18.6.3 Procedure for Handling the Privileged Attention Event                           |     |

| 18.6.4 Procedure for Handling the Lock-Line Reservation Lost Event                     |     |

| 18.6.5 Procedure for Handling the Signal-Notification 1 Available Event                |     |

| 18.6.6 Procedure for Handling the Signal-Notification 2 Available Event                | 481 |

| 18.6.7 Procedure for Handling the SPU Write Outbound Mailbox Available Event           |     |

| 18.6.8 Procedure for Handling the SPU Write Outbound Interrupt Mailbox Available Event | 483 |

| 18.6.9 Procedure for Handling the SPU Decrementer Event                                | 483 |

| 18.6.10 Procedure for Handling the SPU Read Inbound Mailbox Available Event            | 485 |

| 18.6.11 Procedure for Handling the MFC SPU Command Queue Available Event               | 486 |

| 18.6.12 Procedure for Handling the DMA List Command Stall-and-Notify Event             | 486 |

| 18.6.13 Procedure for Handling the Tag-Group Status Update Event                       | 488 |

| 18.7 Developing a Basic Interrupt Handler                                              | 489 |

| 18.7.1 Basic Interrupt Protocol Features and Design                                    | 489 |

| 18.7.2 FLIH Design                                                                     | 490 |

| 18.7.3 SLIH Design and Registering SLIH Functions                                      |     |

| 18.7.4 Example Application Code                                                        | 494 |

| 18.8 Nested Interrupt Handling                                                         | 495 |

| 18.8.1 Nested Handler Design                                                           |     |

| 18.8.2 FLIH Design for Nested Interrupts                                               | 496 |

| 18.9 Using a Dedicated Interrupt Stack                                                 |     |

| 18.10 Sample Applications                                                              |     |

| 18.10.1 SPU Decrementer Event                                                          |     |

| 18.10.2 Tag-Group Status Update Event                                                  |     |

| 18.10.3 DMA List Command Stall-and-Notify Event                                        |     |

| 18.10.4 MFC SPU Command Queue Available Event                                          |     |

| 18.10.5 SPU Read Inbound Mailbox Available Event                                       |     |

| 18.10.6 SPU Signal-Notification Available Event                                        |     |

| 18.10.7 Lock-Line Reservation Lost Event                                               |     |

| 18.10.8 Privileged Attention Event                                                     |     |

| 19. | DMA Transfers and Interprocessor Communication               | 507 |

|-----|--------------------------------------------------------------|-----|

|     | 19.1 Introduction                                            | 507 |

|     | 19.2 MFC Commands                                            | 508 |

|     | 19.2.1 DMA Commands                                          | 510 |

|     | 19.2.2 DMA List Commands                                     | 512 |

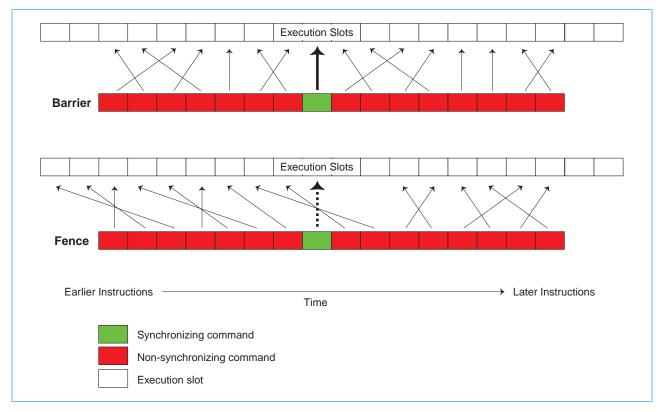

|     | 19.2.3 Synchronization Commands                              | 512 |

|     | 19.2.4 Command Modifiers                                     | 513 |

|     | 19.2.5 Tag Groups                                            | 513 |

|     | 19.2.6 MFC Command Issue                                     | 515 |

|     | 19.2.7 Replacement Class ID and Transfer Class ID            | 515 |

|     | 19.2.8 DMA-Command Completion                                | 516 |

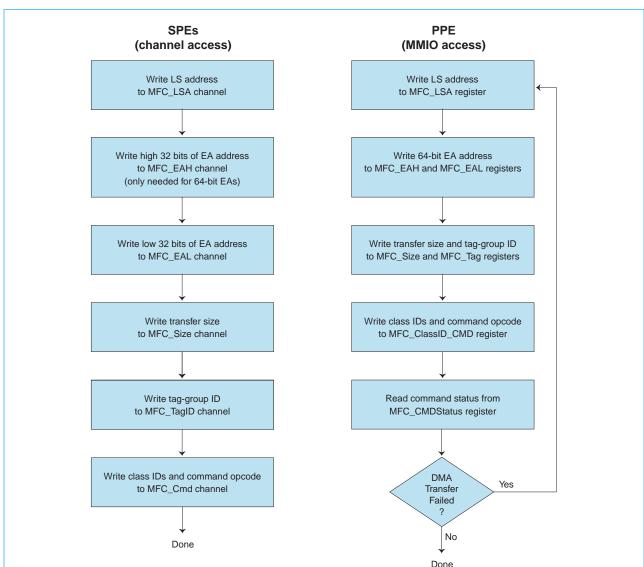

|     | 19.3 PPE-Initiated DMA Transfers                             | 517 |

|     | 19.3.1 MFC Command Issue                                     | 517 |

|     | 19.3.2 MFC Command-Queue Control Registers                   | 519 |

|     | 19.3.3 DMA-Command Issue Status and Errors                   | 519 |

|     | 19.4 SPE-Initiated DMA Transfers                             | 523 |

|     | 19.4.1 MFC Command Issue                                     | 524 |

|     | 19.4.2 MFC Command-Queue Monitoring Channels                 | 525 |

|     | 19.4.3 DMA Command Issue Status and Errors                   | 526 |

|     | 19.4.4 DMA List Command Example                              | 529 |

|     | 19.5 Performance Guidelines for MFC Commands                 | 532 |

|     | 19.6 Mailboxes                                               | 533 |

|     | 19.6.1 Reading and Writing Mailboxes                         | 534 |

|     | 19.6.2 Mailbox Blocking                                      | 534 |

|     | 19.6.3 Dealing with Anticipated Messages                     |     |

|     | 19.6.4 Uses of Mailboxes                                     |     |

|     | 19.6.5 SPU Outbound Mailboxes                                |     |

|     | 19.6.6 SPU Inbound Mailbox                                   | 540 |

|     | 19.7 Signal Notification                                     |     |

|     | 19.7.1 SPU Signalling Channels                               |     |

|     | 19.7.2 Uses of Signaling                                     |     |

|     | 19.7.3 Mode Configuration                                    |     |

|     | 19.7.4 SPU Signal Notification 1 Channel                     |     |

|     | 19.7.5 SPU Signal Notification 2 Channel                     |     |

|     | 19.7.6 Sending Signals                                       |     |

|     | 19.7.7 Receiving Signals                                     |     |

|     | 19.7.8 Differences Between Mailboxes and Signal Notification | 552 |

| 20  | Shared Starage Symphenization                                | EEO |

|     | Shared-Storage Synchronization                               |     |

|     | 20.1 Shared-Storage Ordering                                 |     |

|     | 20.1.1 Storage Model                                         |     |

|     | 20.1.2 PPE Ordering Instructions                             |     |

|     | 20.1.3 SPU Ordering Instructions                             |     |

|     | 20.1.4 MFC Ordering Mechanisms                               |     |

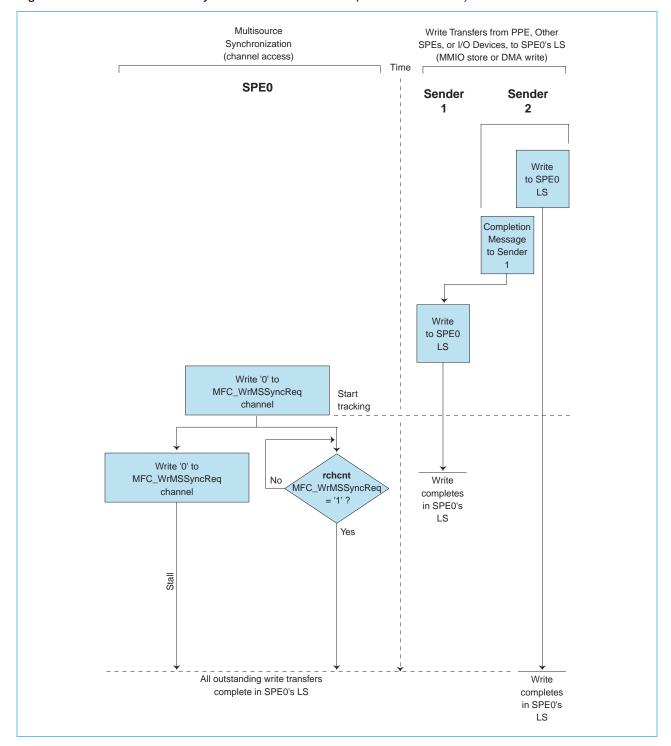

|     | 20.1.5 MFC Multisource Synchronization Facility              |     |

|     | 20.1.6 Scenarios for Using Ordering Mechanisms               |     |

|     | 20.2 PPE Atomic Synchronization                              |     |

|     | 20.2.1 Atomic Synchronization Instructions                   | 5// |

| 21.1 Challenges       6         21.2 Patterns of Parallel Programming       6         21.2.1 Terminology       6         21.2.2 Finding Parallelism       6         21.2.3 Strategies for Parallel Programming       6         21.3.1 Step 1: Understand the Problem       6         21.3.2 Step 2: Choose Programming Tools and Technology       6         21.3.3 Step 3: Develop High-Level Parallelization Strategy       6         21.3.4 Step 4: Develop Low-Level Parallelization Strategy       6         21.3.5 Step 5: Design Data Structures for Efficient Processing       6         21.3.6 Step 6: Iterate and Refine       6         21.3.7 Step 7: Fine-Tune       6         21.4.1 SIMD Parallelization       6         21.4.2 Superscalar Parallelization       6         21.4.3 Hardware Multithreading       6         21.4.4 Multiple Execution Units       6         21.5 Tools for Parallelization       6         21.5.1 Language Extensions: Intrinsics and Directives       6         21.5.2 Compiler Support for Single Shared-Memory Abstraction       6         21.5.3 OpenMP Directives       6         21.5.4 Compiler-Controlled Software Cache       6         21.5.5 Ompiler and Runtime Support for Code Partitioning       6         22.1 SIMD Pasaics                                                                        |    |                                                                                                                |       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------|-------|

| 20.23 SPE Synchronization Primitives       5         20.3 SPE Atomic Synchronization       5         20.3.1 MFC Commands for Atomic Updates       5         20.3.2 The MFC Read Atomic Command Status Channel       5         20.3.3 Avoiding Livelocks       5         20.3.4 Synchronization Primitives       5         21. Parallel Programming       6         21.1 Challenges       6         21.2 Patterns of Parallel Programming       6         21.2.1 Terminology       6         21.2.2 Finding Parallelism       6         21.2.3 Strategies for Parallel Programming       6         21.3.1 Step 1: Understand the Problem       6         21.3.1 Step 1: Understand the Problem       6         21.3.2 Step 2: Choose Programming Tools and Technology       6         21.3.3 Step 3: Develop High-Level Parallelization Strategy       6         21.3.4 Step 4: Develop Low-Level Parallelization Strategy       6         21.3.5 Step 5: Design Data Structures for Efficient Processing       6         21.3.6 Step 6: Iterate and Refine       6         21.3.7 Step 7: Fine-Tune       6         21.4 Levels of Parallelization in the CBE Processor       6         21.4.1 SIMD Parallelization       6         21.4.2 Superscalar Parallelization       6                                                                                  |    | 20.2.2 PPE Synchronization Primitives                                                                          | . 579 |

| 20.3.1 MFC Commands for Atomic Obmand Status Channel       5         20.3.2 The MFC Read Atomic Command Status Channel       5         20.3.3 Avoiding Livelocks       5         20.3.4 Synchronization Primitives       5         21. Parallel Programming       6         21.1 Challenges       6         21.2.1 Terminology       6         21.2.2 Finding Parallelier Programming       6         21.2.2 Finding Parallelier Programming       6         21.2.3 Strategies for Parallel Programming       6         21.3.1 Step 1: Understand the Problem       6         21.3.2 Step 2: Choose Programming Tools and Technology       6         21.3.3 Step 3: Develop High-Level Parallelization Strategy       6         21.3.4 Step 4: Develop Low-Level Parallelization Strategy       6         21.3.5 Step 5: Design Data Structures for Efficient Processing       6         21.3.6 Step 6: Iterate and Refine       6         21.3.7 Step 7: Fine-Tune       6         21.4 Levels of Parallelization       6         21.4.1 SIMD Parallelization       6         21.4.2 Superscalar Parallelization       6         21.4.3 Hardware Multithreading       6         21.4.5 Multiple Execution Units       6         21.5 Tools for Parallelization       6 <td></td> <td></td> <td></td>                                                           |    |                                                                                                                |       |

| 20.3.1 MFC Commands for Atomic Obmand Status Channel       5         20.3.2 The MFC Read Atomic Command Status Channel       5         20.3.3 Avoiding Livelocks       5         20.3.4 Synchronization Primitives       5         21. Parallel Programming       6         21.1 Challenges       6         21.2.1 Terminology       6         21.2.2 Finding Parallelier Programming       6         21.2.2 Finding Parallelier Programming       6         21.2.3 Strategies for Parallel Programming       6         21.3.1 Step 1: Understand the Problem       6         21.3.2 Step 2: Choose Programming Tools and Technology       6         21.3.3 Step 3: Develop High-Level Parallelization Strategy       6         21.3.4 Step 4: Develop Low-Level Parallelization Strategy       6         21.3.5 Step 5: Design Data Structures for Efficient Processing       6         21.3.6 Step 6: Iterate and Refine       6         21.3.7 Step 7: Fine-Tune       6         21.4 Levels of Parallelization       6         21.4.1 SIMD Parallelization       6         21.4.2 Superscalar Parallelization       6         21.4.3 Hardware Multithreading       6         21.4.5 Multiple Execution Units       6         21.5 Tools for Parallelization       6 <td></td> <td>20.3 SPE Atomic Synchronization</td> <td>. 589</td>                       |    | 20.3 SPE Atomic Synchronization                                                                                | . 589 |

| 20.3.2 The MFC Read Atomic Command Status Channel       5         20.3.3 Avoiding Livelocks       5         20.3.4 Synchronization Primitives       5         21. Parallel Programming       6         21.1 Challenges       6         21.2.1 Terminology       6         21.2.2 Finding Parallelism       6         21.2.3 Strategies for Parallel Programming       6         21.3.3 Steps for Parallelizing a Program       6         21.3.1 Step 1: Understand the Problem       6         21.3.2 Step 2: Choose Programming Tools and Technology       6         21.3.3 Step 3: Develop High-Level Parallelization Strategy       6         21.3.4 Step 4: Develop Low-Level Parallelization Strategy       6         21.3.5 Step 5: Design Data Structures for Efficient Processing       6         21.3.5 Step 7: Fine-Tune       6         21.3.7 Step 7: Fine-Tune       6         21.4.1 SIMD Parallelization       6         21.4.1 SIMD Parallelization       6         21.4.2 Superscalar Parallelization       6         21.4.3 Hardware Multithreading       6         21.4.5 Multiple Execution Units       6         21.5.5 Tools for Parallelization       6         21.5.1 Language Extensions: Intrinsics and Directives       6         <                                                                                                  |    |                                                                                                                |       |

| 21. Parallel Programming       6         21.1 Challenges       6         21.2 Patterns of Parallel Programming       6         21.2.1 Terminology       6         21.2.2 Finding Parallelism       6         21.2.3 Strategies for Parallel Programming       6         21.3.1 Steps for Parallelizing a Program       6         21.3.1 Step 1: Understand the Problem       6         21.3.2 Step 2: Choose Programming Tools and Technology       6         21.3.3 Step 3: Develop High-Level Parallelization Strategy       6         21.3.4 Step 4: Develop Low-Level Parallelization Strategy       6         21.3.5 Step 5: Design Data Structures for Efficient Processing       6         21.3.6 Step 6: Iterate and Refine       6         21.3.7 Step 7: Fine-Tune       6         21.4 Levels of Parallelism in the CBE Processor       6         21.4.1 SIMD Parallelization       6         21.4.2 Superscalar Parallelization       6         21.4.3 Hardware Multithreading       6         21.4.4 Multiple Execution Units       6         21.5.5 Compiler Support for Single Shared-Memory Abstraction       6         21.5.1 Compiler Support for Single Shared-Memory Abstraction       6         21.5.5 Compiler and Runtime Support for Code Partitioning       6 <t< td=""><td></td><td></td><td></td></t<>                               |    |                                                                                                                |       |